Science et nature

Le Rôle Clé du Hybrid Bonding dans l’Innovation des Puces 3D

La technologie de hybrid bonding révolutionne l’industrie des semi-conducteurs en permettant des connexions 3D à haute densité entre les puces. Imec a réussi à établir des connexions tous les 400 nanomètres, ouvrant la voie à des processeurs plus puissants malgré le ralentissement de la miniaturisation. Lors de la conférence ECTC, des chercheurs ont présenté des avancées prometteuses, avec des densités atteignant jusqu’à 7 millions de liens par millimètre carré. Cette innovation pourrait transformer la conception des puces, rendant possible des architectures plus complexes et efficaces.

La Technologie de Liaison Hybride : Une Révolution dans les Circuits 3D

La liaison hybride établit des connexions denses en 3D entre les interconnexions en cuivre de deux puces. Imec a réussi à créer des connexions tous les 400 nanomètres.

La Liaison Hybride : Un Élément Clé des Circuits 3D

Les fabricants de puces s’efforcent de maximiser chaque nanomètre disponible pour continuer à réduire la taille des circuits. Cependant, une technologie qui implique des éléments beaucoup plus grands, mesurant des centaines ou des milliers de nanomètres, pourrait avoir un impact tout aussi significatif dans les cinq prochaines années.

Cette technologie, connue sous le nom de liaison hybride, empile deux ou plusieurs puces dans un même boîtier. Cela permet aux fabricants d’augmenter le nombre de transistors dans leurs processeurs et mémoires, malgré un ralentissement général de la réduction des transistors, qui a autrefois été le moteur de la loi de Moore. Lors de la Conférence IEEE sur les Composants Électroniques et la Technologie (ECTC) en mai dernier à Denver, des groupes de recherche du monde entier ont présenté diverses améliorations significatives de cette technologie, certaines montrant des résultats prometteurs pouvant mener à une densité record de connexions entre puces empilées en 3D : environ 7 millions de liaisons par millimètre carré de silicium.

Ces connexions sont essentielles en raison de l’évolution des progrès dans le domaine des semi-conducteurs, comme l’a expliqué Yi Shi d’Intel lors de l’ECTC. La loi de Moore est désormais régie par un concept appelé co-optimisation technologique des systèmes, ou STCO, où les fonctions d’une puce, telles que la mémoire cache, les entrées/sorties et la logique, sont fabriquées séparément en utilisant la meilleure technologie de fabrication pour chacune. La liaison hybride et d’autres technologies d’emballage avancées peuvent ensuite être utilisées pour assembler ces sous-systèmes afin qu’ils fonctionnent aussi efficacement qu’une seule pièce de silicium. Cela n’est possible que si une densité élevée de connexions permet de transférer des données entre les différentes pièces de silicium avec un minimum de retard ou de consommation d’énergie.

Parmi toutes les technologies d’emballage avancées, la liaison hybride offre la plus grande densité de connexions verticales. En conséquence, elle représente le segment à la croissance la plus rapide de l’industrie de l’emballage avancé, selon Gabriella Pereira, analyste technologique et de marché chez Yole Group. Le marché global devrait plus que tripler pour atteindre 38 milliards de dollars américains d’ici 2029, Yole prévoyant que la liaison hybride représentera environ la moitié du marché à ce moment-là, bien qu’elle ne représente actuellement qu’une petite part.

Dans le processus de liaison hybride, des pads en cuivre sont construits sur la face supérieure de chaque puce. Le cuivre est entouré d’une isolation, généralement en oxyde de silicium, et les pads eux-mêmes sont légèrement en retrait par rapport à la surface de l’isolation. Après modification chimique de l’oxyde, les deux puces sont pressées ensemble face à face, de sorte que les pads en retrait s’alignent. Ce sandwich est ensuite lentement chauffé, provoquant l’expansion du cuivre à travers l’espace et fusionnant les deux puces.

La liaison hybride peut soit attacher des puces individuelles d’une taille à une plaquette pleine de puces d’une taille plus grande, soit lier deux plaquettes complètes de puces de même taille. Grâce à son utilisation dans les puces de caméra, ce dernier processus est plus avancé que le premier, selon Pereira. Par exemple, des ingénieurs de l’institut de recherche en microélectronique européen Imec ont créé certaines des liaisons plaquette sur plaquette les plus denses jamais réalisées, avec une distance de liaison de seulement 400 nanomètres. Cependant, Imec n’a réussi qu’une distance de 2 micromètres pour la liaison puce sur plaquette.

Cette avancée représente une amélioration considérable par rapport aux puces 3D avancées actuellement en production, qui ont des connexions espacées d’environ 9 micromètres. C’est également un bond en avant par rapport à la technologie précédente : les « microbumps » de soudure, qui ont des espacements de plusieurs dizaines de micromètres.

« Avec l’équipement disponible, il est plus facile d’aligner plaquette à plaquette que puce à plaquette. La plupart des processus pour la microélectronique sont conçus pour des plaquettes complètes », explique Jean-Charles Souriau, responsable scientifique de l’intégration et de l’emballage à l’organisation de recherche française CEA Leti. Cependant, c’est la technique puce sur plaquette (ou die-to-wafer) qui fait sensation dans les processeurs haut de gamme, comme ceux d’AMD, où cette méthode est utilisée pour assembler les cœurs de calcul et la mémoire cache dans ses CPU avancés et accélérateurs d’IA.

Les chercheurs se concentrent sur l’obtention d’espacements de plus en plus serrés pour les deux scénarios, en visant à rendre les surfaces plus plates, à améliorer l’adhérence des plaquettes entre elles et à réduire le temps et la complexité de l’ensemble du processus. Réussir cette étape pourrait révolutionner la conception des puces.

Des Espacements de Liaison Impressionnants

Les recherches récentes sur la liaison plaquette sur plaquette (WoW) qui ont atteint les espacements les plus serrés, allant de 360 nm à 500 nm, ont nécessité un effort considérable sur un point : la planéité. Pour lier deux plaquettes avec une précision de niveau 100 nm, l’ensemble de la plaquette doit être presque parfaitement plate. Si elle est courbée ou déformée ne serait-ce qu’à un léger degré, des sections entières ne se connecteront pas.

Le processus de planéification des plaquettes est appelé planarisation chimique mécanique, ou CMP. C’est essentiel dans la fabrication de puces, en particulier pour produire les couches d’interconnexions au-dessus des transistors.

« Le CMP est un paramètre clé que nous devons contrôler pour la liaison hybride », déclare Souriau. Les résultats présentés à l’ECTC montrent que le CMP a été porté à un autre niveau, non seulement en aplanissant la plaquette, mais en réduisant les nanomètres de rondeur sur l’isolation entre les pads en cuivre pour garantir de meilleures connexions.

« Il est difficile de dire quelle sera la limite. Les choses avancent très rapidement. » —Jean-Charles Souriau, CEA Leti

D’autres chercheurs se sont concentrés sur la garantie que ces parties aplaties adhèrent suffisamment. Ils ont expérimenté différents matériaux de surface, tels que le carbure de silicium au lieu de l’oxyde de silicium, et ont utilisé différentes méthodes pour activer chimiquement la surface. Au départ, lorsque les plaquettes ou les dies sont pressés ensemble, ils sont maintenus en place par des liaisons hydrogène relativement faibles, et la préoccupation est de savoir si tout restera en place lors des étapes de traitement ultérieures. Après l’attachement, les plaquettes et les puces sont lentement chauffées, dans un processus appelé recuit, pour former des liaisons chimiques plus solides. La force de ces liaisons et même la manière de l’évaluer ont été au cœur de nombreuses recherches présentées à l’ECTC.

Une partie de la force de cette liaison finale provient des connexions en cuivre. L’étape de recuit permet au cuivre de s’étendre à travers l’espace pour former un pont conducteur. Contrôler la taille de cet espace est crucial, explique Seung Ho Hahn de Samsung. Une expansion trop faible et le cuivre ne fusionnera pas. Une expansion trop importante et les plaquettes seront repoussées. Cela se joue à quelques nanomètres, et Hahn a rapporté des recherches sur un nouveau processus chimique qu’il espère utiliser pour obtenir le bon résultat en gravant le cuivre une seule couche atomique à la fois.

La qualité de la connexion est également primordiale. Les métaux dans les interconnexions des puces ne sont pas un cristal unique ; ils sont constitués de nombreux grains, des cristaux orientés dans différentes directions. Même après l’expansion du cuivre, les frontières des grains du métal ne traversent souvent pas d’un côté à l’autre. Une telle traversée devrait réduire la résistance électrique d’une connexion et améliorer sa fiabilité. Des chercheurs de l’Université de Tohoku au Japon ont rapporté un nouveau schéma métallurgique qui pourrait enfin générer de grands grains uniques de cuivre traversant la frontière. « C’est un changement radical », déclare Takafumi Fukushima, professeur associé à Tohoku. « Nous analysons maintenant ce qui le sous-tend. »

D’autres expériences discutées à l’ECTC se sont concentrées sur l’optimisation du processus de liaison. Plusieurs ont cherché à réduire la température de recuit nécessaire pour former des liaisons, généralement autour de 300 °C.

Avancées dans le domaine du Bonding Hybride des Puces

Des chercheurs d’Applied Materials ont récemment fait des progrès significatifs dans une méthode visant à réduire considérablement le temps nécessaire pour l’annealing, le faisant passer de plusieurs heures à seulement 5 minutes. Cette avancée pourrait minimiser les risques de dommages aux puces causés par une exposition prolongée à la chaleur.

Les Innovations du Bonding CoW

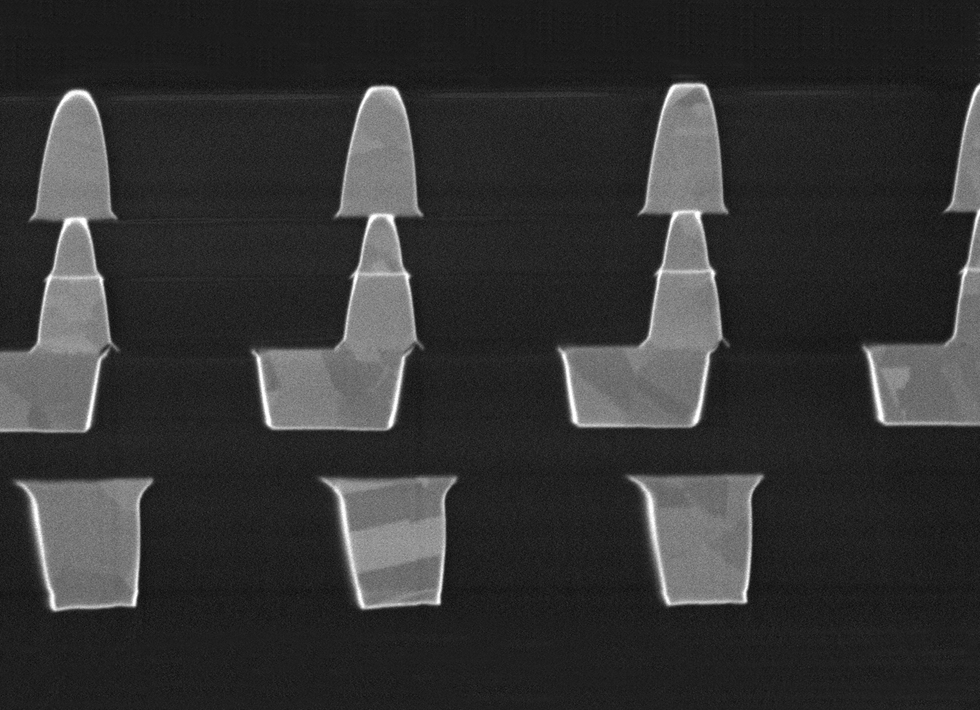

Imec a utilisé la gravure plasma pour découper des puces et leur donner des coins chanfreinés, ce qui réduit le stress mécanique pouvant nuire aux connexions.Imec

Imec a utilisé la gravure plasma pour découper des puces et leur donner des coins chanfreinés, ce qui réduit le stress mécanique pouvant nuire aux connexions.Imec

Le bonding hybride chip-on-wafer (CoW) est particulièrement bénéfique pour les fabricants de CPU et de GPU avancés. Cette technique permet aux concepteurs de superposer des chiplets de tailles variées et de tester chaque puce avant de les assembler, évitant ainsi de compromettre un CPU coûteux avec une seule pièce défectueuse.

Cependant, le CoW présente des défis similaires à ceux du wafer-on-wafer (WoW), tout en offrant moins d’options pour les surmonter. Par exemple, le CMP est conçu pour aplatir les wafers, mais pas les dies individuels. Une fois que les dies ont été découpés et testés, il reste peu de solutions pour améliorer leur préparation au bonding.

Malgré cela, des chercheurs d’Intel ont rapporté des liaisons hybrides CoW avec un pas de 3 µm, tandis qu’une équipe d’Imec a réussi à atteindre 2 µm, principalement en rendant les dies très plats tout en restant attachés au wafer et en maintenant une propreté rigoureuse tout au long du processus. Les deux groupes ont utilisé la gravure plasma pour découper les dies, évitant ainsi les éclats aux bords qui pourraient créer des débris nuisibles aux connexions. Cette méthode a également permis à l’équipe d’Imec de façonner les dies avec des coins chanfreinés, réduisant ainsi le stress mécanique susceptible de rompre les connexions.

Le Rôle Crucial du Bonding Hybride dans la Mémoire à Haute Bande Passante

Le bonding hybride CoW sera essentiel pour l’avenir de la mémoire à haute bande passante (HBM), selon plusieurs chercheurs présents à l’ECTC. L’HBM est une superposition de dies DRAM, actuellement de 8 à 12 dies de hauteur, sur une puce de logique de contrôle. Souvent intégrée dans le même package que les GPU haut de gamme, l’HBM est indispensable pour gérer le flux massif de données nécessaire au fonctionnement de modèles de langage volumineux comme ChatGPT. Actuellement, les dies HBM sont empilés à l’aide de la technologie des microbumps, qui consiste en de petites billes de soudure entourées d’un matériau organique entre chaque couche.

Avec la demande croissante en mémoire due à l’IA, les fabricants de DRAM envisagent d’empiler 20 couches ou plus dans les puces HBM. Le volume occupé par les microbumps signifie que ces empilements deviendront bientôt trop hauts pour s’adapter correctement dans le package avec les GPU. Le bonding hybride permettrait de réduire la hauteur des HBM et faciliterait également l’évacuation de la chaleur excédentaire du package, car il y aurait moins de résistance thermique entre ses couches.

« Je pense qu’il est possible de créer un empilement de plus de 20 couches avec cette technologie. » —Hyeonmin Lee, Samsung

Lors de l’ECTC, des ingénieurs de Samsung ont démontré que le bonding hybride pouvait produire un empilement HBM de 16 couches. « Je pense qu’il est possible de créer un empilement de plus de 20 couches avec cette technologie », déclare Hyeonmin Lee, ingénieur senior chez Samsung. D’autres nouvelles technologies CoW pourraient également faciliter l’intégration du bonding hybride dans la mémoire à haute bande passante. Des chercheurs de CEA Leti explorent ce qu’on appelle la technologie d’auto-alignement, selon Souriau. Cela permettrait d’assurer de bonnes connexions CoW en utilisant uniquement des processus chimiques. Certaines parties de chaque surface seraient rendues hydrophobes et d’autres hydrophiles, créant ainsi des surfaces qui s’aligneraient automatiquement.

À l’ECTC, des chercheurs de l’Université de Tohoku et de Yamaha Robotics ont rapporté des travaux sur un schéma similaire, utilisant la tension de surface de l’eau pour aligner des pads de 5 µm sur des puces DRAM expérimentales avec une précision supérieure à 50 nm.

Les Perspectives du Bonding Hybride

Les chercheurs continueront sans aucun doute à réduire le pas des connexions de bonding hybride. Un pas de 200 nm en WoW n’est pas seulement possible, mais souhaitable, a déclaré Han-Jong Chia, chef de projet chez Taiwan Semiconductor Manufacturing Co., aux ingénieurs de l’ECTC. Dans les deux prochaines années, TSMC prévoit d’introduire une technologie appelée livraison d’énergie par l’arrière. (Intel prévoit de faire de même d’ici la fin de cette année.) Cette technologie place les interconnexions d’alimentation volumineuses du chip sous la surface du silicium plutôt qu’au-dessus. Avec ces conduits d’alimentation dégagés, les niveaux supérieurs peuvent mieux se connecter à des pads de bonding hybride plus petits, selon les calculs des chercheurs de TSMC. La livraison d’énergie par l’arrière avec des pads de bonding de 200 nm réduirait tellement la capacitance des connexions 3D que l’efficacité énergétique et la vitesse du signal pourraient être jusqu’à huit fois meilleures que celles obtenues avec des pads de 400 nm.

Le bonding hybride chip-on-wafer est plus avantageux que le bonding wafer-on-wafer, car il permet de placer des dies d’une taille sur un wafer de dies plus grands. Cependant, la densité des connexions réalisables est inférieure à celle du bonding wafer-on-wafer.Imec

Le bonding hybride chip-on-wafer est plus avantageux que le bonding wafer-on-wafer, car il permet de placer des dies d’une taille sur un wafer de dies plus grands. Cependant, la densité des connexions réalisables est inférieure à celle du bonding wafer-on-wafer.Imec

À l’avenir, si les pas de bonding continuent à se réduire, Chia suggère qu’il pourrait devenir pratique de « plier » des blocs de circuits pour qu’ils soient construits sur deux wafers. Cela permettrait à certaines connexions actuellement longues au sein du bloc de prendre un raccourci vertical, ce qui pourrait accélérer les calculs et réduire la consommation d’énergie.

De plus, le bonding hybride pourrait ne pas se limiter au silicium. « Aujourd’hui, il y a beaucoup de développement dans les wafers silicium-silicium, mais nous cherchons également à réaliser un bonding hybride entre des wafers de nitrure de gallium et de silicium ainsi que des wafers en verre… tout sur tout », déclare Souriau de CEA Leti. Son organisation a même présenté des recherches sur le bonding hybride pour des puces de calcul quantique, impliquant l’alignement et le bonding de niobium supraconducteur au lieu de cuivre.

« Il est difficile de dire quelle sera la limite », conclut Souriau. « Les choses évoluent très rapidement. »

Général

Une éruption mystérieuse qui a changé le climat et rendu le soleil bleu : découverte d’une île reculée du Pacifique

Une découverte fascinante a été faite par des chercheurs concernant une éruption volcanique survenue en 1831, qui a modifié le climat et rendu le soleil bleu. En étudiant les cendres dans les carottes de glace polaires, ils ont identifié le Zavaritskii, un volcan isolé des îles Kouriles, comme responsable de cet événement mystérieux. Cette éruption a entraîné un refroidissement climatique de 1 °C, provoquant des famines en Inde et au Japon. William Hutchison, volcanologue à l’Université de St Andrews, souligne que cette découverte révèle encore combien nous ignorons sur l’activité volcanique dans cette région reculée.

Découverte des Origines d’une Éruption Volcanique Historique

Des chercheurs ont récemment élucidé les origines d’une éruption volcanique survenue il y a 200 ans, qui a libéré une quantité massive de soufre dans l’atmosphère, entraînant un changement climatique notable et donnant au soleil une teinte bleue.

Un refroidissement Climatique en 1831

En 1831, la température moyenne dans l’hémisphère nord a chuté d’environ 1,8 degré Fahrenheit (soit environ 1 degré Celsius), coïncidant avec des rapports faisant état de conditions météorologiques sombres et de variations colourées du soleil. Bien que les scientifiques aient établi qu’une éruption volcanique majeure était à l’origine de ce phénomène étrange, le volcan responsable demeurait inconnu jusqu’à présent.

Pistes Découvertes dans les Cœurs Glaciaires

Afin d’identifier la source de cette éruption, les chercheurs ont analysé des cendres retrouvées dans des carottes glaciaires polaires. Leur étude a révélé que l’éruption provenait du volcan Zavaritskii situé sur l’île isolée de Simushir,qui fait partie des îles Kouriles contestées entre la Russie et le Japon. Pendant la guerre froide, l’Union soviétique avait utilisé un cratère volcanique inondé sur Simushir comme base secrète pour sous-marins nucléaires.

Les résultats publiés le 30 décembre 2024 dans la revue PNAS, soulignent combien il reste encore à découvrir concernant l’activité volcanique sur ces îles.

L’impact Météorologique Documenté

« Bien que 1831 soit une période relativement récente, nous n’avions aucune idée que ce volcan était à l’origine [de cette éruption dramatique] », a déclaré William Hutchison, auteur principal et volcanologue à l’Université St Andrews. « C’était complètement hors radar. »

L’éruption de 1831 fait partie d’une série d’éruptions volcaniques au XIXe siècle liées à la phase finale du Petit Âge Glaciaire, qui s’étendait approximativement entre 1800 et 1850. Ce phénomène n’était pas véritablement une période glaciaire — celle-ci ayant pris fin il y a environ dix mille ans — mais représentait néanmoins le moment le plus froid enregistré au cours des cinq derniers siècles.

Météo Dévastatrice en Europe

D’après Hutchison,il n’existe pas de témoignages écrits directs relatant cette éruption en raison du caractère éloigné et peu habité des îles Kouriles souvent enveloppées par un épais brouillard. Cependant, son impact est bien documenté : le compositeur allemand Felix Mendelssohn évoquait un été « désolé » en traversant les Alpes où les températures étaient « aussi froides qu’en hiver ». De nombreux récits rapportent également que le soleil prenait des teintes bleues ou violettes dues aux particules aérosols émises par le panache du volcan. Un phénomène similaire avait été observé après l’éruption du Krakatoa en 1883.

Dérives Mortelles Potentielles

L’éventuelle conséquence mortelle liée à cette éruption pourrait avoir été significative : une baisse globale des températures aurait précédé plusieurs famines majeures en Inde et au Japon durant les années 1830. Hutchison souligne : « Nous savons qu’avec de grandes éruptions volcaniques comme celle-ci, lorsque vous avez un refroidissement climatique cela entraîne aussi des modifications dans les précipitations ainsi que dans les rendements agricoles. » Cela peut engendrer une pénurie alimentaire pour la population.

Mise en Évidence Scientifique Cruciale

Afin d’identifier précisément la source de cet événement cataclysmique passé, Hutchison et son équipe ont examiné les résidus cendreux présents dans diverses carottes glaciaires datant du XIXe siècle prélevées au Groenland. La composition chimique correspondante aux cendres trouvées indiquait clairement leur origine commune avec celles provenant notamment du Japon voisin; cependant ils ont rapidement exclu ce pays comme site potentiel étant donné sa densité démographique élevée ainsi qu’un historique bien documenté concernant ses propres activités volcaniques.

Cela a conduit leurs recherches vers les îles Kouriles.

Sensation ‘Eureka’

L’équipe scientifique découvrit alors que la composition chimique présente aux dépôts cendreux issus du volcano Zavaritskii correspond parfaitement avec celle retrouvée dans ces carottes glaciaires; Hutchison qualifie cela comme étant un moment ‘Eureka’, semblable à celui où on trouve une empreinte digitale lors d’une enquête criminelle.

« C’était vraiment une journée fantastique, » se remémore-t-il avec enthousiasme; « l’une des meilleures journées passées au laboratoire. »

Alerte Manquante Sur Les Volcans Actuels

Tandis qu’ils avaient résolu ce mystère historique lié à l’éruption de 1831 , Hutchison note cependant qu’il n’existe toujours aucun système instrumentalisé surveillant activement toute activité potentielle autour des volcans situés aux îles Kouriles — situation valable pour bon nombre autres volcans autour globe.

« Si cette même éruption devait se produire aujourd’hui, » conclut-il prudemment ; « je ne pense pas que nous serions beaucoup mieux préparés comparativement à notre situation durant année 1831. » Cela illustre combien il sera difficile prédire quand ou où pourrait surgir prochainement un autre événement majeur susceptible modifier notre climat. »

Science et nature

La « reine des loups » de Yellowstone tuée par une meute rivale après 11 ans de vie et 10 portées de louveteaux

Le parc national de Yellowstone a perdu l’une de ses habitantes les plus emblématiques : Wolf 907F, surnommée la « Reine des Loups ». À 11 ans, cette louve au regard unique avait déjà donné naissance à un incroyable nombre de 10 portées. Sa longévité exceptionnelle et son rôle de matriarche en faisaient une figure légendaire. Malheureusement, après une confrontation avec un groupe rival le jour de Noël, sa vie s’est éteinte. Malgré les défis qu’elle a affrontés, Wolf 907F a su mener sa meute avec force et détermination jusqu’à la fin.

Le parc national de Yellowstone a perdu l’un de ses habitants les plus emblématiques et résilients : une louve d’un œil, âgée de 11 ans, qui avait réalisé un exploit en donnant naissance à 10 portées au cours de sa longue vie.

Connue sous le nom affectueux de « Reine des Loups » pour son rôle prépondérant au sein du groupe Junction Butte, la louve 907F est décédée le jour de Noël (25 décembre 2024) suite à une confrontation avec un autre groupe rival.

La louve 907F a vécu plus du double de l’espérance de vie habituelle des loups gris dans le parc, qui est généralement comprise entre quatre et cinq ans. Sa longévité et son statut de matriarche en ont fait une figure légendaire dans l’écosystème du parc ainsi qu’auprès des passionnés d’animaux sauvages.

les événements ayant conduit à sa mort ont débuté le 22 décembre, lorsque la louve 907F et ses petits se nourrissaient d’une carcasse de bison sur la rive nord du fleuve Yellowstone, d’après Cowboy State Daily.Des membres du groupe rival Rescue Creek — habituellement confinés sur la rive sud — ont traversé le fleuve sans prévenir et se sont engagés dans une violente altercation avec le groupe dirigé par 907F.

Bien que la louve ait survécu à cette première rencontre, ses blessures se sont révélées fatales. Son collier radio, surveillé par les biologistes du parc Yellowstone, a signalé son immobilité le 26 décembre, indiquant qu’elle était probablement décédée la veille.

Une des plus anciennes louves de Yellowstone

Avec ses onze années passées dans ce milieu sauvage depuis leur réintroduction en 1995 au parc national yellowstone,d’après Smithsonian Magazine, elle faisait partie des six rares spécimens ayant atteint cet âge avancé.

Louve courageuse face aux défis rencontrés tout au long de sa vie. Les scientifiques pensent qu’elle aurait perdu son œil gauche vers l’âge four; cependant, les raisons exactes demeurent floues. de plus, elle avait survécu à un épisode sévère dû à la gale — maladie cutanée contagieuse causée par des acariens microscopiques pouvant être mortels.

Même face aux adversités rencontrées tout au long des années passées en tant que leader efficace pour son groupe familial , elle a réussi à donner naissance encore une fois lors du printemps dernier (2024), surprenant ainsi les chercheurs par sa vitalité malgré son âge avancé.

Ayant mis bas chaque année durant toute une décennie avant sa mort dès qu’elle atteignit maturité sexuelle , Rabe affirmait auprès du Cowboy State Daily que cela faisait d’elle « la femelle ayant connu le succès reproductif sans précédent dans toute l’histoire connue ».

Science et nature

Les meilleures offres du MacBook Pro ce mois-ci !

Apple a récemment dévoilé ses nouveaux modèles de MacBook Pro de 14 et 16 pouces, équipés des puissants processeurs M4, M4 Pro et M4 Max. Ces modèles améliorés, lancés en novembre 2024, offrent le double de RAM par rapport à leurs prédécesseurs. Si vous envisagez d’acheter un MacBook Pro, sachez que les anciens modèles M3 sont désormais en liquidation avec des remises intéressantes. Cependant, attention à la différence de RAM ! Découvrez nos conseils pour dénicher les meilleures offres et faire le choix parfait pour vos besoins.

Les Nouveaux Modèles de MacBook Pro : Ce Qu’il Faut Savoir

En octobre 2024, Apple a dévoilé ses derniers modèles de MacBook Pro de 14 et 16 pouces, équipés des puces M4, M4 Pro et M4 Max. Ces nouvelles versions arrivent un an après le lancement des variantes M3, qui avaient déjà fait sensation. Les nouveaux modèles offrent une double capacité de RAM par rapport à leurs prédécesseurs.

Les ventes ont débuté le vendredi 8 novembre et les appareils sont désormais disponibles à l’achat.

Acheter un MacBook Pro : Faut-il opter pour les anciens modèles ?

Si vous envisagez d’acheter un MacBook Pro, vous pourriez être tenté par les modèles de la série M3 qui pourraient bénéficier de réductions alors que les revendeurs écoulent leur stock.Cependant, gardez à l’esprit que ces anciens modèles disposent d’une moitié moins de RAM que les nouveaux. Apple facture environ 200 $/200 £ pour une mise à niveau de la RAM au moment de l’achat ; il est donc essentiel que toute réduction sur un ancien modèle prenne cela en compte. De plus, si vous êtes en dehors des États-Unis, notez que le prix des nouveaux modèles peut être inférieur à celui des anciens.

avec une combinaison d’augmentations et diminutions tarifaires dans toute la gamme par rapport aux générations précédentes, il peut s’avérer difficile d’identifier une bonne affaire. Heureusement, notre équipe d’experts apple scrute Internet tout au long de l’année pour dénicher les meilleures offres sur le MacBook pro ainsi que sur le MacBook Air qui présente également plusieurs similitudes avec son homologue pro.

Comparaison des Prix Actuels

Vous trouverez ci-dessous des tableaux comparatifs affichant les meilleurs prix actuels pour chaque modèle standard du MacBook Pro (y compris ceux mis en vente depuis le 8 novembre). Des offres sont également disponibles pour certains modèles désormais discontinués tant qu’ils restent en stock chez divers détaillants.

Aperçu des Meilleures Offres Actuelles

- M4 – MacBook Pro 14 pouces :

- Amazone : modèle avec 512 Go/16 Go RAM – $1,459 (140 $ off)

- Amazone : Modèle avec 1 To/24 Go RAM – $1,819 (180 $ off)

- Amazone : Modèle M4 Pro avec 1 To/24 Go RAM – $2,179 (220 $ off)

- Amazone : Modèle M4 Max avec 16 pouces – À partir de $3,174 (325 $ off)

Détails Sur Les Offres Discontinuées

- M3 – ancien modèle :

- B&H photo: Modèle avec 512 Go/18 Go RAM – Environ $1,599 (-400$)

- Best Buy: Version précédente du modèle pro – Environ $2,199 (-300$)

L’Importance D’un Guide D’Achat Complet

Pour obtenir davantage d’informations et choisir votre ordinateur portable Apple idéalement adapté à vos besoins spécifiques ou professionnels , consultez notre guide complet où nous abordons tous les différents types disponibles ainsi qu’un guide spécifique aux achats concernant toute la gamme Macintosh.

Démarche Pour Acquérir Un Nouveau Produit Apple

Tandis qu’il est possible d’acquérir directement auprès d’Apple ou via divers revendeurs agréés dans le monde entier — beaucoup offrant aussi bien sur produits neufs qu’anciens — il vaut toujours mieux comparer avant achat afin maximiser vos économies potentielles ! Vous pouvez consulter nos recommandations concernant où acheter votre prochain appareil Macintosh ici même !

Détaillants Recommandés Aux États-Unis :

- Boutique officielle Apple

- Boutique Éducation Apple

- Amazone

< li>B&H Photo < li > Best Buy < / li >< li > Walmart < / li >< / ul >

< h r >

< h r >

< p > Si vous recherchez encore plus moyen économe , découvrez si acheter vos produits électroniques depuis un autre pays pourrait réduire considérablement votre budget .< / p >

< h r >

< h r >

< h o u t e s t i n g = "u k retailers" >Détaillants Recommandés Au Royaume-Uni:

< ul >< li > Boutique officielle Apple< / li >< li > Boutique Éducation Apple< / li >< li > Amazone< / li >< < ...

-

Business2 ans ago

Business2 ans agoComment lutter efficacement contre le financement du terrorisme au Nigeria : le point de vue du directeur de la NFIU

-

Général2 ans ago

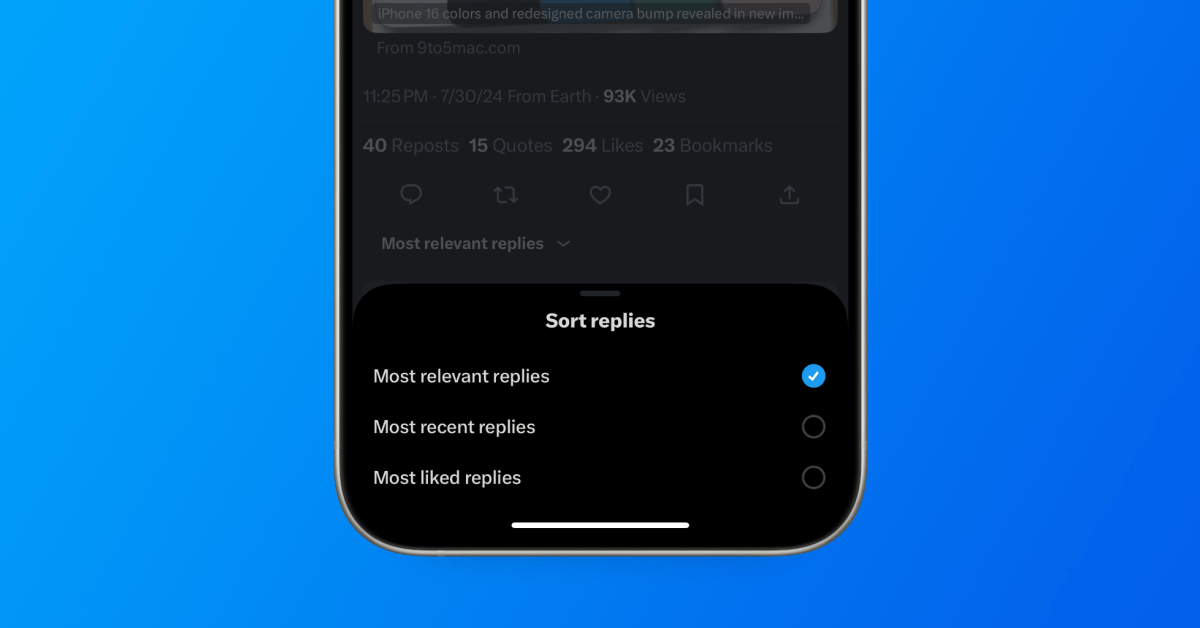

Général2 ans agoX (anciennement Twitter) permet enfin de trier les réponses sur iPhone !

-

Technologie1 an ago

Technologie1 an agoTikTok revient en force aux États-Unis, mais pas sur l’App Store !

-

Général1 an ago

Général1 an agoAnker SOLIX dévoile la Solarbank 2 AC : la nouvelle ère du stockage d’énergie ultra-compatible !

-

Général1 an ago

Général1 an agoLa Gazelle de Val (405) : La Star Incontournable du Quinté d’Aujourd’hui !

-

Sport1 an ago

Sport1 an agoSaisissez les opportunités en or ce lundi 20 janvier 2025 !

-

Business1 an ago

Business1 an agoUne formidable nouvelle pour les conducteurs de voitures électriques !

-

Science et nature1 an ago

Science et nature1 an agoDes Projets Ambitieux qui Pourraient Redéfinir la Géopolitique