Général

RePalm : Vers le premier port non autorisé de PalmOS !

rePalm Photo Album(constantly updated) Table of Contents A LARGE warning! PalmOS Architecture (and a bit of history) History Modules? Libraries? DALs? Drivers? Towards the first unauthorized PalmOS port So what’s so hard? ROM formats are hard So write a DAL and you’re done! Minimal DAL Drawing is hard Theft is a form of flattery, right?

Technologie : Un Avertissement Majeur !

Cet article présente un projet en phase de pré-lancement. Je mettrai à jour le contenu et le projet, ce qui signifie que ce document n’est pas figé. Si vous souhaitez suivre les modifications, c’est à vous de le faire. Je m’engage simplement à fournir une liste des changements en bas de l’article.

Architecture de PalmOS : Un Peu d’Histoire

Historique

Avant la version 5.4, PalmOS stockait toutes les données en RAM sous forme de bases de données. Ces bases de données se divisaient en deux catégories : les bases de données d’enregistrement (comme on pourrait l’imaginer) et les bases de données de ressources (similaires aux ressources de MacOS classique). Chaque base de données possédait un type et un identifiant de créateur, chacun étant un entier de 32 bits, généralement constitué de caractères ASCII. En règle générale, chaque application créait des bases de données avec son propre identifiant de créateur. Certains types avaient également une signification particulière, par exemple, « appl » désignait une application.

Modules, Bibliothèques, DALs et Pilotes

L’architecture de PalmOS repose sur divers composants, notamment des modules, des bibliothèques, des DALs (Data Abstraction Layers) et des pilotes. Ces éléments interagissent pour permettre aux applications de fonctionner de manière fluide sur le système d’exploitation.

Vers le Premier Port Non Autorisé de PalmOS

Qu’est-ce qui rend cela si difficile ?

Le portage de PalmOS sur d’autres plateformes présente de nombreux défis. Les formats de ROM sont complexes, et il est nécessaire de développer un DAL pour faciliter l’interaction avec le matériel. Cela peut sembler simple, mais la réalité est bien plus compliquée.

Les Formats de ROM

Les formats de ROM sont un véritable casse-tête. Chaque appareil a ses propres spécificités, ce qui complique le processus de portage. Il est essentiel de comprendre quel type de ROM est utilisé pour chaque appareil afin de garantir la compatibilité.

Écriture d’un DAL Minimal

Créer un DAL minimal est une étape cruciale. Cela permet de simplifier les interactions entre le système d’exploitation et le matériel, mais cela nécessite une compréhension approfondie des deux.

La Difficulté du Dessin

Le dessin sur des appareils PalmOS peut s’avérer complexe. Les limitations matérielles et les spécificités du système d’exploitation rendent cette tâche ardue.

La Controverse de l’Imitation

L’imitation méticuleuse peut être perçue comme une forme de flatterie, mais elle soulève également des questions éthiques. La frontière entre l’inspiration et le plagiat est souvent floue dans le domaine de la technologie.

La Carte SD Virtuelle

L’utilisation d’une carte SD virtuelle est une solution innovante pour contourner certaines limitations des appareils PalmOS. Cela permet d’étendre les capacités de stockage sans nécessiter de matériel supplémentaire.

Quel ROM Utilisez-vous ?

La question de la ROM utilisée est essentielle. Chaque appareil a ses propres caractéristiques, et il est crucial de s’assurer que le portage fonctionne correctement sur le matériel cible.

Alors, C’est Fini ? Ça Fonctionne ?

Une fois toutes ces étapes franchies, il est temps de tester le portage. Cela peut sembler simple, mais de nombreux problèmes peuvent survenir à ce stade.

Vers le Premier Appareil PalmOS Pirate

Un Aperçu des Appareils PalmOS 5.x

Les appareils PalmOS 5.x, avec leurs processeurs ARM, ont marqué une avancée significative dans l’évolution de la technologie mobile. Ces appareils ont ouvert la voie à de nouvelles possibilités, mais ils présentent également des défis uniques.

ARMv7M

L’architecture ARMv7M est un élément clé dans le développement de nouveaux appareils. Sa puissance et son efficacité en font un choix privilégié pour les développeurs.

Et Si Nous Essayions ?

Face aux défis, il est toujours possible d’explorer de nouvelles avenues. L’innovation est souvent le résultat de l’expérimentation.

Le Développement sur Matériel : Un Défi

CortexEmu à la Rescousse

CortexEmu est un émulateur qui facilite le développement sur du matériel PalmOS. Il permet aux développeurs de tester leurs applications sans avoir besoin d’un appareil physique.

Mais Vous Aviez Promis du Matériel Réel

Le passage au développement sur du matériel réel peut être frustrant. Les bugs matériels peuvent entraver le processus de développement et nécessiter des ajustements constants.

La Nécessité d’un Noyau

Pourquoi Pas Linux ?

L’utilisation de Linux comme noyau pour le développement de PalmOS est une option intéressante. Cela permet de bénéficier d’une base solide tout en explorant de nouvelles fonctionnalités.

Les Défis du Code ARM

Le Code ARM : Un Problème Persistant

Le code ARM reste un défi majeur lors du portage. Les différences d’architecture peuvent entraîner des complications inattendues.

Écrire un Émulateur en C : Est-ce Lent ?

La question de la vitesse est cruciale. Écrire un émulateur en C peut sembler lent, mais des optimisations peuvent améliorer les performances.

Est-ce Suffisamment Rapide Maintenant ?

Après de nombreuses itérations, il est essentiel de tester la rapidité de l’émulateur. Les performances doivent être à la hauteur des attentes des utilisateurs.

Le Travail d’un JIT n’est Jamais Terminé

LDM et STM : Un Cauchemar à Jamais !

Les instructions LDM et STM peuvent poser de nombreux problèmes lors de l’émulation. Leur complexité nécessite une attention particulière.

Instructions Conditionnelles et Sauts

Les instructions conditionnelles et les sauts sont des éléments clés à prendre en compte lors de l’émulation. Leur gestion correcte est essentielle pour garantir le bon fonctionnement des applications.

La Rapidité de PACE

Les Sauts Indirects

Les sauts indirects peuvent ralentir le processus d’émulation. Il est crucial de trouver des solutions adaptées à ce problème.

Une Solution Spéciale pour un Problème Particulier

Trouver des solutions spécifiques à des problèmes particuliers est une compétence essentielle pour les développeurs.

Histoires de Reverse Engineering de PalmOS

Support de la Carte SD

Le support des cartes SD est un aspect important du développement de PalmOS. Cela permet d’étendre les capacités de stockage des appareils.

Support du Port Série

Le port série est un autre élément clé. Il permet la communication entre les appareils et peut être testé par les développeurs.

Support de la Connectivité

Le développement de la connectivité est en cours. Les défis sont nombreux, mais les avancées sont prometteuses.

Support Audio

Le support audio est un domaine complexe. La gestion de l’audio sur PalmOS nécessite des compétences techniques avancées.

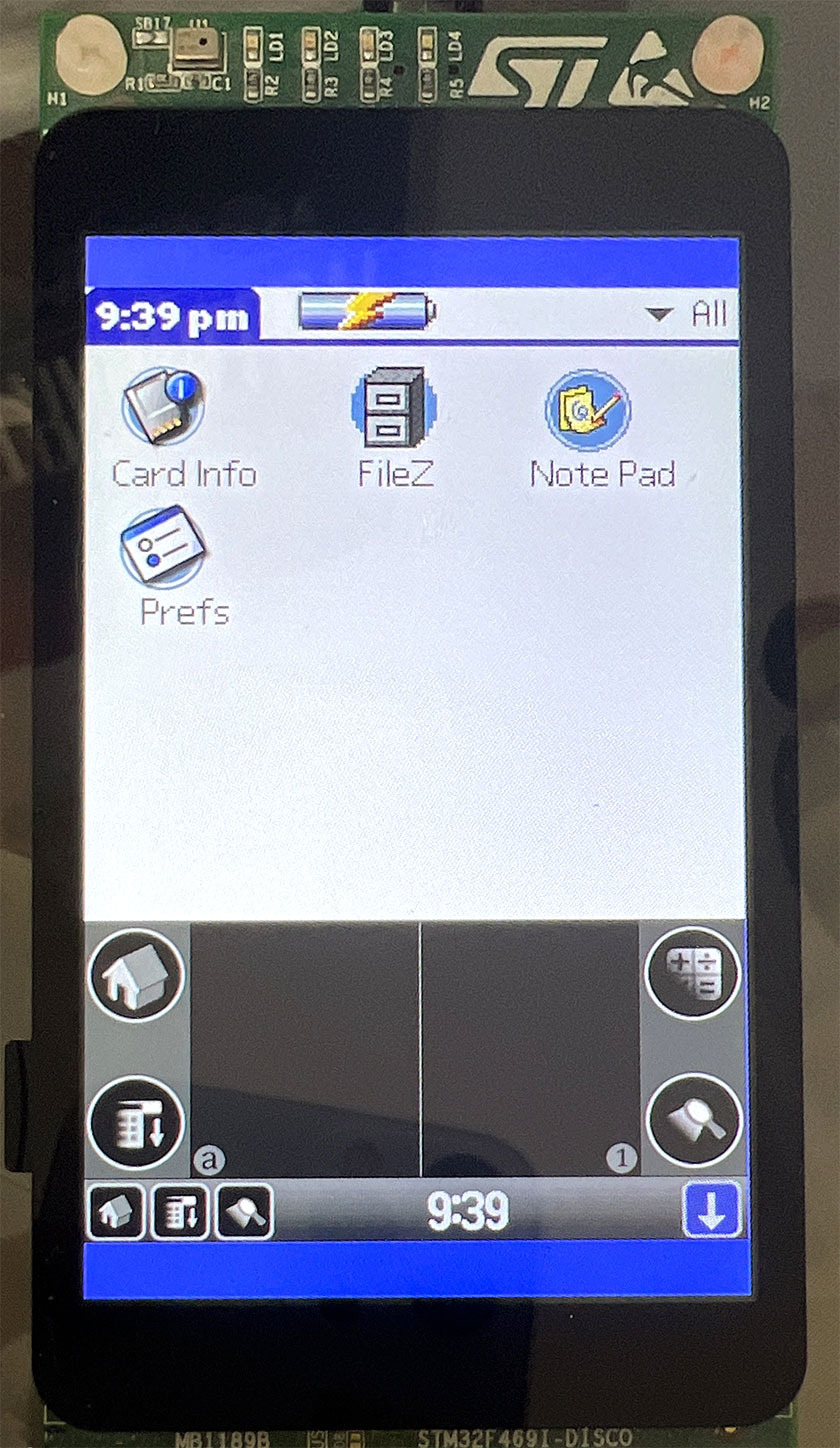

Matériel Réel : reSpring

L’Accessoire Ultime pour Springboard

reSpring est un accessoire innovant qui améliore les fonctionnalités des appareils PalmOS. Son développement a nécessité une attention particulière aux détails.

Interfaçage avec le Visor

L’interfaçage avec le Visor est une étape cruciale pour garantir la compatibilité avec les appareils existants.

Conclusion : Où en Sommes-Nous ?

Le développement autour de PalmOS continue d’évoluer. Les défis sont nombreux, mais les opportunités d’innovation sont également présentes. Les développeurs doivent rester attentifs aux évolutions technologiques pour tirer le meilleur parti de cette plateforme.

Le système d’exploitation PalmOS a été initialement conçu pour fonctionner sur des processeurs Motorola 68k, et ce, depuis ses débuts jusqu’à la version 4.x. Avec l’arrivée de la version 5, Palm Inc a décidé de migrer vers des processeurs ARM, offrant ainsi des performances nettement supérieures. Cependant, cette transition posait un défi majeur : que faire des applications déjà existantes ? De nombreuses applications PalmOS avaient été développées pour la version 4.x et compilées pour le processeur m68k. Pour résoudre ce problème, Palm Inc a introduit le PACE (Palm Application Compatibility Extension). Ce système interceptait les appels système, tels que SysAppLaunch, et émulait le processeur m68k, permettant ainsi aux anciennes applications de fonctionner sur la nouvelle architecture. Lorsqu’une application m68k effectuait un appel système, PACE traduisait les paramètres et appelait l’API native ARM, garantissant ainsi une exécution rapide des applications, même si leur logique était émulée. En effet, les appareils PalmOS 4.x fonctionnaient généralement à 33 MHz, tandis que les appareils PalmOS 5.x atteignaient des vitesses de plusieurs centaines de MHz, ce qui minimisait les ralentissements. Cela était suffisant pour Palm Inc, car de nombreuses applications intégrées, comme le calendrier et les contacts, restaient des applications m68k.

Il est à noter que Palm Inc n’a jamais fourni de documentation sur la création d’applications ARM natives complètes pour PalmOS 5.x. Bien que cela fût possible, les meilleures pratiques n’étaient pas documentées. La méthode officielle pour tirer parti de la vitesse des nouveaux processeurs ARM consistait à utiliser l’appel système PceNativeCall pour accéder à un petit morceau de code ARM natif, que Palm Inc appelait « ARMlet » puis « PNOlet ». Palm recommandait de n’utiliser cette méthode que pour les parties de code les plus critiques, et il était relativement difficile d’effectuer des appels système depuis ce code natif, nécessitant un retour vers PACE pour gérer les paramètres.

PalmOS 5.x a conservé de nombreux aspects de la conception de PalmOS 4.x, tels que le tas partagé, l’absence de mémoire protégée et le manque de documentation sur le multithreading. Une nouveauté de cette version était le support des modules chargés dynamiquement. En fait, chaque application ou bibliothèque ARM native dans PalmOS 5.x est un module, chacun ayant un identifiant unique dans la plage de 0 à 1023. Cela explique probablement pourquoi Palm Inc n’a jamais documenté la création d’applications natives complètes, car cela aurait limité le nombre d’applications à 1024.

Modules, bibliothèques et pilotes

Le noyau du système d’exploitation, la gestion de la mémoire, la plupart des pilotes et la gestion bas niveau du processeur sont assurés par le DAL (Device Abstraction Layer). Le DAL (Module ID 0) exporte environ 200 appels système, selon la version de PalmOS. Ces appels concernent des fonctions de bas niveau, telles que l’état de la batterie, l’accès brut aux primitives de dessin à l’écran, la gestion des modules, etc. Au-dessus du DAL se trouve le module Boot (Module ID 1), qui fournit de nombreux appels système orientés utilisateur. Ce module inclut des gestionnaires pour les données, la mémoire, les alarmes, les échanges, les bitmaps et les fenêtres. Enfin, le module UI (Module ID 2) offre toutes les primitives d’interface utilisateur, telles que les contrôles, les formulaires, les menus et les tableaux. Ensemble, ces trois modules constituent le cœur de PalmOS, et il serait même possible de démarrer un ROM contenant uniquement ces fichiers.

Ces trois premiers modules sont spéciaux, car ils sont toujours chargés et leurs fonctions exportées sont accessibles via un raccourci particulier. Pour les modules 0, 1 et 2, il est possible d’appeler une fonction exportée en exécutant deux instructions spécifiques. Ce raccourci facilite les appels aux fonctions système par les modules natifs, mais ne s’applique pas aux autres modules. Il est également possible de modifier ces tables de pointeurs de fonction, ce qui a souvent été fait par ce que l’on appelait des « hacks », et cela est également utilisé par le système d’exploitation lui-même.

PalmOS ne dispose d’aucune protection mémoire, ce qui signifie que tout code utilisateur peut accéder au matériel. Cela est exploité par des pilotes, comme ceux des cartes SD, qui sont généralement des modules séparés et non intégrés au DAL. Le module Boot charge toutes les bases de données de ressources PalmOS de certains types au démarrage, permettant leur initialisation. Parmi ces types, on trouve les pilotes de slot, les pilotes de système de fichiers, les pilotes de port série, et d’autres extensions. Cette séparation est pratique, car elle permet de remplacer ou de retirer facilement ces modules, bien qu’il existe des cas particuliers que les développeurs de PalmOS n’avaient pas anticipés.

Technologie vers le premier port non autorisé de PalmOS

Quelles sont les difficultés rencontrées ?

Comme mentionné précédemment, aucune documentation sur l’API native de PalmOS 5.x n’a jamais été publiée. Un petit nombre de personnes a réussi à comprendre certaines parties, mais personne n’a réussi à tout saisir. Cela est en partie dû au fait que de nombreuses fonctionnalités ne sont pas pertinentes pour un développeur d’applications, ce qui a limité l’intérêt. Cela pose un problème pour ceux qui souhaitent créer un nouvel appareil. J’ai donc dû effectuer beaucoup de rétro-ingénierie pour ce projet, en explorant des API ennuyeuses que je devais tout de même mettre en œuvre. De plus, il me fallait un noyau et du matériel fonctionnel.

Les formats de ROM sont complexes

Pour commencer, j’ai développé un outil permettant de décomposer et de reconstruire des images de ROM PalmOS. Le format est assez complexe et a évolué entre les versions, mais après de nombreux efforts, l’outil « splitrom » peut désormais décomposer avec succès une ROM PalmOS allant des appareils pré-version 1.0 jusqu’aux ROMs PalmOS 6.0 Cobalt. L’outil « mkrom » peut également produire des images valides de PalmOS 5.x, bien que je n’aie pas cherché à créer d’autres versions, car cela ne m’était pas nécessaire. À ce stade, j’ai pris un détour dans le projet pour collecter des ROM PalmOS.

Exploration des Défis de Développement d’un DAL

Après avoir acquis une expérience significative avec divers appareils et prototypes, j’ai décidé de partager mes découvertes. Mon processus a commencé par l’analyse d’un ROM T|T3, où j’ai remplacé certains fichiers, réassemblé le tout et reflashé mon T|T3. À ma grande surprise, il a démarré ! C’était prometteur.

Écrire un DAL : Une Étape Cruciale

Ne disposant d’aucun matériel pour effectuer des tests, ni d’un noyau à utiliser, j’ai dû agir rapidement. La solution la plus efficace que j’ai trouvée était d’utiliser un processeur ARM réel avec un noyau existant, en l’occurrence Linux. Comme mon ordinateur de bureau est basé sur un processeur x86, j’ai eu recours à QEMU. J’ai développé un DAL rudimentaire qui enregistrait chaque fonction appelée avant de provoquer un crash intentionnel. Au démarrage, il se comportait comme le DAL de PalmOS : il chargeait Boot et appelait PalmOSMain dans un nouveau thread. J’ai ensuite créé une application simple qui utilisait mmap() pour mapper une zone de mémoire à un emplacement spécifique, soutenue par « rom.bin » et « ram.bin », et j’ai tenté de la démarrer. J’ai obtenu quelques messages de journalisation et un crash, comme prévu. Cela semblait prometteur, mais j’ai réalisé que la plupart des fonctions étaient nécessaires pour le démarrage. Une journée décevante…

Construction d’un DAL Minimal

Après plusieurs mois de travail, j’ai réussi à implémenter la majorité du DAL, qui fonctionnait dans mon « runner » sous QEMU. C’était une configuration complexe. Étant donné que tout cela se déroulait dans un espace utilisateur sous Linux, je devais faire appel au « runner » pour des tâches comme la création de threads. C’était un véritable casse-tête. Le code actuel de rePalm prend encore en charge ce mode, mais je ne prévois pas de l’utiliser fréquemment pour diverses raisons. Par exemple, le noyau Linux ne dispose pas de certaines API essentielles à PalmOS, comme la possibilité de désactiver et de réactiver le changement de tâche. PalmOS demande parfois que la préemption soit désactivée, ce que Linux ne permet pas. De plus, PalmOS nécessite la capacité de mettre en pause et de reprendre un thread à distance, sans le consentement de celui-ci. La bibliothèque pthreads ne permet pas non plus cela. J’ai bricolé quelques solutions avec ptrace, mais c’était chaotique. Anecdote amusante : comme ma machine est multi-cœur et que je n’ai jamais défini d’affinités, c’était la première fois que PalmOS fonctionnait sur un appareil multi-cœur. Je ne m’en suis rendu compte que bien plus tard, mais c’était plutôt cool, non ?

Les Défis du Dessin

Un problème majeur est apparu. Pour une raison quelconque, des opérations telles que dessiner des lignes, des rectangles, des cercles et des bitmaps faisaient toutes partie du DAL. Bien que dessiner une ligne ne soit pas compliqué, des instructions comme « dessiner un rectangle arrondi avec une couleur de premier plan X et une couleur de fond Y, en utilisant le mode de dessin ‘masque’ sur ce canevas » ou « afficher cette image compressée en 16 bits couleur pleine à 144 ppi sur ce canevas de 4 bits par pixel à 108 ppi avec dithering, en respectant les couleurs de transparence, et en utilisant le mode ‘inverser' » deviennent rapidement complexes. Et oui, le DAL était censé gérer tout cela. Bien sûr, rien de tout cela n’était documenté ! C’était un véritable cauchemar. Au début, j’ai traité toutes les fonctions de dessin comme des NOP et j’ai simplement enregistré le texte dessiné pour suivre l’avancement de mon démarrage. Cela m’a permis de mettre en œuvre de nombreuses autres OsCalls que le DAL devait fournir, mais j’ai finalement dû me confronter à la nécessité de dessiner. Ma première approche a été de mettre en œuvre les choses moi-même, en me basant sur les noms de fonction et un peu d’ingénierie inverse. Cette méthode a échoué rapidement – la matrice des possibilités était tout simplement trop vaste. Il y a 8 modes de dessin, 3 densités supportées, 4 formats de compression d’image, 5 profondeurs de couleur supportées et deux formats de police. Il était impossible de tout envisager, surtout sans moyen de s’assurer que j’avais raison. Je ne suis pas sûr que certains de ces modes aient jamais été utilisés par un logiciel existant, mais peu importe - il fallait que ce soit pixel par pixel exact ! Que faire ?

Une Inspiration Contestable

J’ai décidé d’adopter une solution temporaire. J’ai désassemblé le DAL du Zire72. J’ai copié chacune des fonctions nécessaires, ainsi que toutes les fonctions qu’elles appelaient, et ainsi de suite. J’ai ensuite nettoyé leurs références directes aux variables globales du Zire DAL et entre elles, et j’ai regroupé le tout dans un énorme fichier « drawing.S ». Ce fichier contenait plus de 30 000 lignes, et je n’avais en grande partie aucune idée de son fonctionnement. Ou de son efficacité…

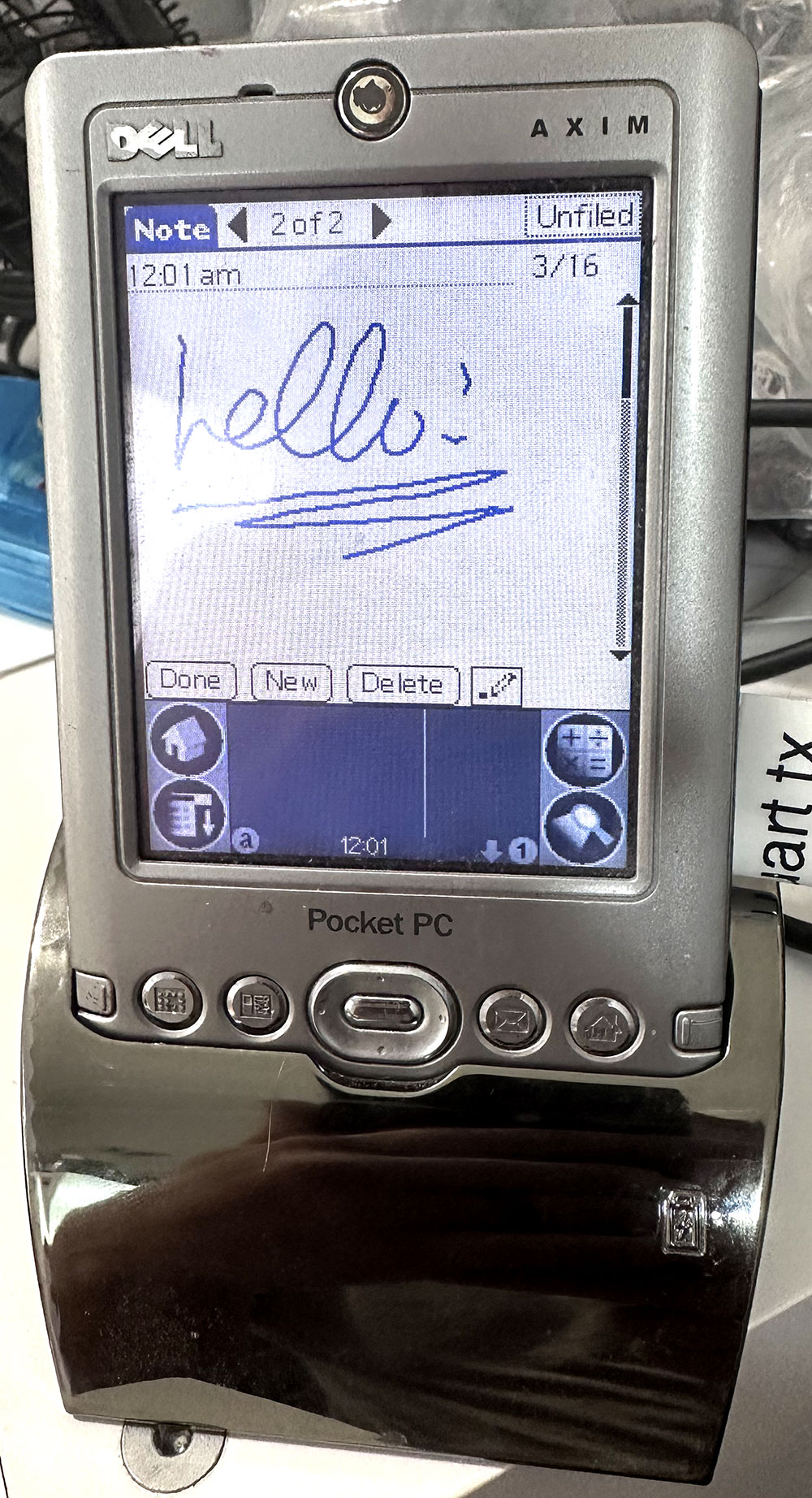

Et pourtant, cela a fonctionné ! Pas immédiatement, bien sûr, mais cela a fonctionné. Les couleurs étaient déformées, des artefacts apparaissaient partout, mais j’ai réussi à voir l’écran de calibration de l’écran tactile après le démarrage ! Succès, n’est-ce pas ? Eh bien, pas du tout. En fait, il s’est avéré qu’en raison d’optimisations, le code de dessin de PalmOS interagissait directement avec les variables globales du pilote d’affichage. À ce stade, mon « pilote » d’affichage n’était qu’une zone de mémoire soutenue par une surface SDL. Cela a nécessité beaucoup de travail (un travail inutile – le pire genre) pour comprendre ce qu’il recherchait et lui fournir ce dont il avait besoin. Mais après quelques semaines supplémentaires, le code de dessin du DAL du Zire72 fonctionnait sous rePalm, et j’ai pu voir les éléments dessinés correctement. Après avoir mis en place un support rudimentaire pour l’écran tactile, j’ai même pu interagir avec le dispositif virtuel et voir l’écran d’accueil. Super, mais tout cela était vain. Je ne possède pas ce code et je ne peux pas le distribuer. Je ne peux pas non plus l’améliorer, l’étendre, le corriger ou même prétendre le comprendre entièrement. Ce n’était pas une voie à suivre.

Une Réécriture Méticuleuse

Il était temps de passer à l’action. J’ai réécrit le code de dessin. Fonction par fonction. Ligne par ligne. Instruction par instruction. J’ai testé chaque fonction après l’avoir remplacée du mieux que je pouvais. En cours de route, j’ai acquis une compréhension de la manière dont PalmOS dessine, des raccourcis pour les cas courants, etc. Cet effort a duré deux mois, et à la fin, 30 000 lignes d’assemblage non commentées se sont transformées en 8 000 lignes de C. rePalm était enfin redevenu entièrement mon propre code ! Au passage, j’ai optimisé quelques éléments et ajouté le support pour une densité d’un et demi, une fonctionnalité que le DAL du Zire72 ne supportait pas. Parmi toutes les parties de ce projet, c’était la plus difficile à réaliser, car à la fin de chaque fonction décodée, comprise et réécrite, il n’y avait pas de progrès visible – l’objectif était simplement de ne rien casser, et il y avait toujours des dizaines de milliers de lignes de code à désassembler, comprendre et réécrire en C.

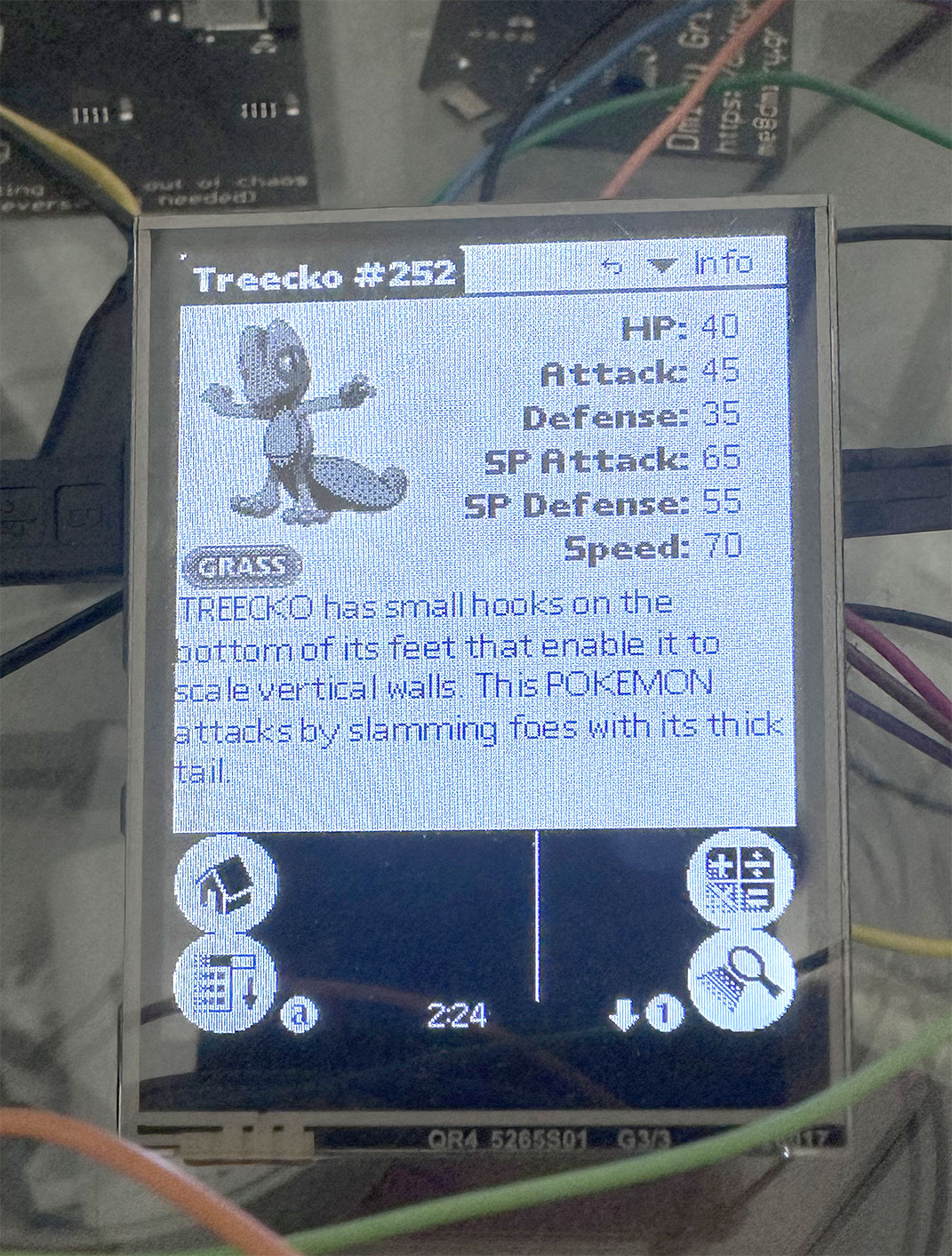

Création d’une Carte SD Virtuelle

Pour faciliter les tests, il serait pratique de pouvoir charger des programmes plus facilement dans l’appareil plutôt que de les intégrer dans le ROM. J’ai développé un pilote de slot personnalisé qui ne faisait rien d’autre que de permettre l’utilisation de mon système de fichiers personnalisé. Ce système de fichiers utilisait des hyper-appels pour accéder au code dans le « runner » afin d’effectuer des opérations de système de fichiers sur l’hôte. En gros, cela a créé un dossier partagé entre mon PC et rePalm. J’ai utilisé cela pour vérifier que la plupart des logiciels et des jeux fonctionnaient comme prévu.

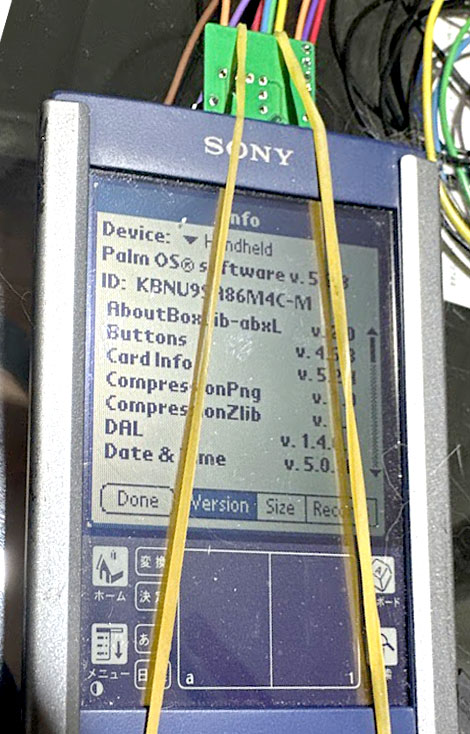

Compatibilité des ROMs de Dispositifs

Je pouvais tester n’importe quelle ROM ! J’ai essayé l’image pré-production de Tungsten T, l’image de LifeDrive, et même la ROM de Sony TH55 a démarré ! Bien qu’il y ait eu des ajustements spécifiques à chaque appareil et à chaque version de l’OS, j’ai réussi à les appliquer automatiquement au moment de l’exécution. Par exemple, déterminer quelle version de l’OS était en cours d’exécution se faisait facilement en examinant le nombre de points d’entrée exportés de Boot. De plus, identifier si la ROM était un appareil Sony était simple en recherchant le module SonyDAL. Dans ce cas, nous refusons de la charger et exportons nous-mêmes des fonctions équivalentes. Pourquoi le DAL a-t-il besoin de connaître la version de l’OS ? Certains points d’entrée du DAL ont changé entre PalmOS 5.0 et PalmOS 5.2, et PalmOS 5.4 ou ultérieur attend des comportements supplémentaires de certaines fonctions existantes que nous devons prendre en charge.

Et maintenant, c’est fini, n’est-ce pas ?

Vers la création du premier appareil PalmOS pirate

Comprendre le fonctionnement des appareils PalmOS 5.x

Pour saisir les défis rencontrés, il est essentiel d’explorer le fonctionnement des appareils PalmOS 5.x. Ces dispositifs étaient conçus pour des processeurs ARMv4T ou ARMv5, avec une capacité de mémoire flash ou ROM variant de 4 à 32 Mo, et une RAM allant de 8 à 128 Mo pour les allocations en temps réel et le stockage de données. La version 5.4 de PalmOS a introduit le NVFS, que nous allons ignorer pour l’instant, comme beaucoup d’entre nous l’ont souhaité à l’époque de sa sortie. Les processeurs ARMv4T et ARMv5 utilisaient deux ensembles d’instructions distincts : ARM et Thumb. Les instructions ARM mesurent chacune exactement 4 octets et constituent l’ensemble d’instructions original pour les processeurs ARM. En revanche, Thumb, introduit avec la version v4T, visait à améliorer la densité du code en utilisant des instructions de 2 octets, permettant ainsi de réduire la taille du code. Cependant, cette optimisation avait un coût : les instructions Thumb nécessitaient souvent plus d’étapes pour accomplir les mêmes tâches, et elles avaient accès à moins de registres que leurs homologues ARM, ce qui pouvait entraîner un code moins optimal. Malgré cela, de larges portions de PalmOS étaient compilées en mode Thumb, car la vitesse n’était pas toujours un facteur déterminant. À l’inverse, Sony avait choisi de compiler l’ensemble de son système d’exploitation en mode ARM, profitant de puces flash plus grandes.

Les défis de la commutation entre ARM et Thumb

La commutation entre les modes ARM et Thumb dans les processeurs ARMv5 se faisait par certaines instructions qui modifiaient le flux de contrôle. Étant donné que toutes les instructions ARM mesurent 4 octets et sont alignées sur une frontière de 4 octets, toute adresse d’instruction ARM valide a ses deux derniers bits à zéro. Les instructions Thumb, quant à elles, mesurent 2 octets et ont donc leur dernier bit à zéro. Cela a permis d’utiliser cette caractéristique pour la commutation de mode. L’instruction BX vérifiait le bit inférieur du registre de destination : s’il était à 1, la destination était considérée comme Thumb, sinon comme ARM. D’autres instructions, comme POP et LDR, fonctionnaient de la même manière. Cependant, l’architecture ARMv5 est désormais obsolète, l’architecture ARM ayant évolué jusqu’à la version v8.x, qui propose des registres de 64 bits et un ensemble d’instructions totalement différent. Bien que les cartes de développement ARMv7 soient abondantes et peu coûteuses, leur documentation est souvent insuffisante, rendant leur utilisation complexe sans un noyau Linux.

Exploration des microcontrôleurs ARM

Une alternative intéressante était d’explorer les microcontrôleurs, qui sont largement disponibles, bien documentés et économiques. ARM propose une gamme de cœurs sous la marque Cortex, tels que Cortex-M0, M3 et M4, qui utilisent un ensemble d’instructions Thumb/Thumb2. Ces cœurs sont adaptés pour des tâches complexes, prenant en charge des opérations de multiplication étendues et des flux de contrôle sophistiqués. Cependant, un inconvénient majeur est que ces microcontrôleurs ne prennent en charge que les instructions Thumb, ce qui limite l’exécution de nombreuses fonctionnalités de PalmOS, car chaque bibliothèque doit être entrée en mode ARM. Cela posait un problème significatif pour l’exécution d’un système d’exploitation non modifié.

Une solution innovante pour l’intégration de PalmOS

Face à ces limitations, j’ai décidé d’étendre le format de module de PalmOS pour permettre une entrée directe en mode Thumb. J’ai également modifié le chargeur de modules pour qu’il reconnaisse les points d’entrée des bibliothèques pointant vers un simple thunk ARM vers Thumb, ce qui a permis un démarrage presque complet sans nécessiter de mode ARM. Cependant, cette solution n’était pas suffisante, car de nombreuses parties du système d’exploitation restaient en mode ARM, notamment des fonctions essentielles comme MemMove et MemCmp. L’objectif de faire fonctionner un PalmOS non modifié restait donc un défi de taille.

Défis de l’architecture ARM

Dans le domaine des systèmes d’exploitation et des applications, la possibilité d’éditer tout et n’importe où était limitée. Certaines fonctionnalités pouvaient être ajustées via SysPatchEntry. J’ai ainsi optimisé les fonctions MemMove et MemCmp pour améliorer la vitesse, en fournissant des implémentations optimales pour Thumb2. Cependant, d’autres éléments, comme la division entière (qui n’est pas prise en charge par ARMv5), étaient disséminés dans presque toutes les bibliothèques et ne pouvaient pas être modifiés car ils n’étaient pas exportés. Nous avions réellement besoin d’un environnement capable d’exécuter des instructions ARM.

Exploration des possibilités

Que se passerait-il si nous tentions de passer un microcontrôleur ARMv7M en mode ARM ? Le manuel est très explicite à ce sujet. Il CHANGERA le mode, effacera le bit d’état indiquant que nous sommes en mode Thumb, et lorsqu’il tentera d’exécuter l’instruction suivante, il déclenchera une UsageFault car il ne peut pas fonctionner dans ce mode. L’instruction Thumb BLX qui change toujours de mode est indéfinie dans ARMv7M, et si elle est exécutée, le processeur générera également une UsageFault, signalant une instruction invalide. Bien que cela semble décourageant, c’est en réalité une excellente nouvelle ! Nous pouvons intercepter une UsageFault… Si vous comprenez où je veux en venir et que cela vous horrifie, merci de votre attention ! Nous reviendrons sur cette intrigue plus tard pour permettre à tout le monde de se mettre à jour.

Technologie : Le besoin de matériel

CortexEmu : La solution

J’avais l’intention de faire fonctionner tout cela sur une puce de classe Cortex-M, mais je ne voulais pas développer directement sur celle-ci – c’était trop lent et frustrant. De plus, je n’ai trouvé aucun bon émulateur pour les puces de classe Cortex-M. À ce stade, j’ai pris une pause de deux semaines pour créer CortexEmu. Cet émulateur fonctionnel pour Cortex-M0/M3/M23 reproduit fidèlement le matériel Cortex. Il dispose d’un stub GDB pour le débogage, d’une émulation matérielle rudimentaire pour afficher un écran, et prend en charge un RTC, une console et un écran tactile. Il gère les modes privilégiés et non privilégiés, et émule également l’unité de protection de la mémoire (MPU). CortexEmu reste le meilleur moyen de développer rePalm.

Attendez ! Vous avez promis du matériel réel

Oui, oui, nous y arriverons, mais cela prendra encore plusieurs mois dans l’histoire, alors soyez patients !

Technologie : La nécessité d’un noyau

Pourquoi ne pas utiliser Linux ?

PalmOS nécessite un noyau avec un ensemble particulier de primitives. Nous avons déjà abordé certaines (mais pas toutes) des raisons pour lesquelles Linux est un choix peu judicieux. De plus, la version Linux compatible avec Cortex-M3 est lente ET volumineuse, ce qui en fait une option inacceptable. Alors, quelle alternative avons-nous ?

J’ai finalement décidé d’écrire mon propre noyau. Il est simple et fonctionne bien. Il peut s’exécuter sur n’importe quel processeur de classe Cortex-M, prend en charge le multithreading avec priorités, des minuteries précises, des mutex, des sémaphores, des groupes d’événements, des boîtes aux lettres, et toutes les primitives que PalmOS exige, comme la possibilité de suspendre des threads et de désactiver le changement de tâche. Il utilise également le MPU pour ajouter des mesures de sécurité de base, comme des gardes de pile. De plus, il offre un excellent support pour le stockage local des threads, ce qui sera utile par la suite. Pourquoi créer mon propre noyau alors qu’il en existe déjà tant ? Aucun des noyaux disponibles ne possédait vraiment les primitives dont j’avais besoin, et les ajouter aurait pris tout autant de temps.

Technologie : Les défis du code ARM

Le code ARM reste problématique

PalmOS ne parvenait toujours pas à démarrer complètement jusqu’à l’interface utilisateur à cause du code ARM. Mais, comme je l’ai mentionné précédemment, nous pouvons intercepter les tentatives d’accès au mode ARM. J’ai donc écrit un gestionnaire de UsageFault pour cela, puis… je l’ai émulé.

Vous ne voulez pas dire… ?

Oh, mais si. J’ai développé un émulateur ARM qui lit chaque instruction et l’exécute, jusqu’à ce que le code sorte du mode ARM, moment auquel je quitte l’émulation pour reprendre l’exécution native. Les détails de ce fonctionnement sont fascinants, car l’émulateur nécessite sa propre pile et ne peut pas s’exécuter sur la pile du code émulé. Il doit également y avoir un espace pour stocker les registres émulés, car nous ne pouvons pas simplement les garder dans les registres réels (il n’y a pas assez de registres pour les deux). Quitter l’émulation est également un défi, car il faut charger tous les registres et le registre d’état en une seule opération atomique. Ce n’est pas trivial sur Cortex-M. Quoi qu’il en soit, « emu.c » et « emuC.c » contiennent le code – n’hésitez pas à explorer.

Écrire un émulateur en C n’est pas lent ?

Vous n’avez aucune idée ! L’émulateur était effectivement lent. J’ai instrumenté CortexEmu pour compter les cycles et j’ai constaté qu’il fallait en moyenne 170 cycles du processeur hôte pour émuler une seule instruction ARM. Ce n’était pas suffisant. Il est bien connu que les émulateurs écrits en C sont lents. Les compilateurs C ne sont pas très efficaces pour optimiser le code des émulateurs. Que faire alors ? J’ai donc réécrit le cœur de l’émulateur en assembleur. En fait, je l’ai fait deux fois : une fois pour ARMv7M (cible Cortex-M3) et une fois pour ARMv6M (cible Cortex-M0). La vitesse s’est considérablement améliorée. Pour le cœur M3, j’atteignais en moyenne 14 cycles par instruction, et pour le M0, 19. Une performance d’émulateur très respectable, si je puis me permettre de le dire.

Est-ce assez rapide maintenant ?

Comme mentionné précédemment, sur les appareils PalmOS d’origine, le code ARM était généralement plus rapide que le code Thumb, donc la plupart des routines les plus critiques étaient écrites en ARM. Pour nous, le code ARM est 14 fois plus lent que le code Thumb. Ainsi, le code censé être le plus rapide est devenu lent. Mais examinons ce code de plus près. Les routines de division en font partie. ARMv7M gère la division en matériel, mais ARMv5 ne le faisait pas (et ARMv6M non plus). Ces routines prennent environ une centaine de cycles en mode ARM. Les fonctions MemMove, MemMSet et MemCmp dont nous avons déjà parlé ne nous préoccupent pas car nous les avons remplacées, mais de nombreuses bibliothèques avaient leurs propres copies internes que nous ne pouvons pas modifier. Je suppose que le compilateur préfère en général intégrer ses propres « memset » et « memcpy ». Cela représentait une grande partie de l’utilisation du code ARM lors du processus de démarrage. Heureusement, toutes ces fonctions sont identiques partout…

Pouvons-nous donc identifier certaines de ces fonctions dans le code de l’émulateur et exécuter des routines natives plus rapides ? J’ai fait cela et le temps de démarrage a effectivement diminué. Le coût moyen par instruction a augmenté en raison de l’identification, mais le temps de démarrage a été réduit. Super. Mais que se passe-t-il après le démarrage ? Après le démarrage, nous rencontrons le véritable défi… l’émulateur m68k de PACE est écrit en ARM. 60 kilooctets de code clairement écrit à la main avec de nombreuses astuces astucieuses. Ces astuces deviennent problématiques lorsque vous devez les émuler… Cela signifie que chaque application m68k (qui est la plupart d’entre elles) fonctionne désormais sous double émulation. Pas idéal… Et aussi : lent. Il fallait agir. J’ai envisagé de réécrire PACE, mais cela n’est pas une solution viable – il existe de nombreuses bibliothèques ARM et je ne peux pas toutes les réécrire. De plus, comment puis-je prétendre exécuter un système d’exploitation non modifié si je remplace chaque élément ?

Il existe une autre méthode pour rendre le code non natif plus rapide…

Technologie : Une solution innovante

Traduction à la volée

PACE contient beaucoup de code statique très sollicité. Sur les appareils réels, il réside dans la ROM et ne change pas. La plupart des bibliothèques sont identiques. Que pouvons-nous faire pour améliorer la vitesse d’exécution ? Les traduire en un format que nous pouvons exécuter nativement, bien sûr. La plupart des gens hésiteraient à entreprendre seuls la tâche d’écrire un traducteur à la volée. Mais cela ne fait que parce qu’ils sont…

Introduction aux JIT : Comment démarrer ?

Pour initier un JIT, nous procédons de manière similaire à celle utilisée pour un émulateur. Nous mettons en place un cache de traduction par thread (CT) qui stockera nos traductions. Pourquoi par thread ? Cela permet d’éviter que l’un d’eux ne purge le cache pendant qu’un autre est en cours d’exécution, ce qui pourrait entraîner des problèmes. Le CT contiendra des unités de traduction (UT), chacune représentant un code traduit. Chaque UT inclut l’adresse ARM d’origine et le code Thumb2 valide. De plus, une table de hachage sera utilisée pour associer les adresses »ARM » d’origine à un seau où la première UT correspondant à cette valeur de hachage est stockée. Chaque seau est une liste chaînée, et nous utilisons 4096 seaux, un chiffre configurable. Un hachage rapide et simple est appliqué, et les tests sur un échantillon représentatif d’adresses ont montré une bonne distribution. Ainsi, chaque fois qu’un UsageFault se produit, indiquant une tentative d’entrée en mode ARM, nous consultons la table de hachage pour l’adresse souhaitée. En cas de succès, nous remplaçons simplement le PC dans le cadre d’exception par le pointeur « code » de l’UT correspondante et continuons l’exécution du code natif rapidement. Parfait ! Que se passe-t-il si nous n’obtenons pas de correspondance ? Nous sauvegardons alors l’état et remplaçons le PC dans le cadre d’exception par l’adresse du code de traduction (nous ne voulons pas traduire en mode noyau).

Comprendre les instructions ARM

Le front-end d’un JIT doit essentiellement ingérer les instructions ARM et les interpréter. Nous allons intercepter celles que nous ne comprenons pas et tenter de traduire toutes celles que nous maîtrisons. Cependant, nous rencontrons un premier obstacle. Certains jeux utilisent des instructions non valides. Par exemple, le jeu « Bejeweled » contient du code ARM qui tente d’exécuter LDMDB R11, {R0-R12, SP, PC}^. Ignorons le fait que R0-R2 et R12 n’ont pas besoin d’être sauvegardés, ce qui est inefficace, et notons que cette instruction n’est pas valide en mode utilisateur. Le petit symbole caret à la fin signifie « transférer également SPSR vers CPSR« . Cette demande est invalide en mode utilisateur, et le manuel de référence de l’architecture ARM précise clairement que son exécution en mode utilisateur aura des effets indéfinis. Cela explique pourquoi Bejeweled ne fonctionnait pas sous rePalm avec QEMU, qui a correctement refusé d’exécuter cette instruction. J’ai donc sorti un appareil Palm d’un tiroir pour tester ce qui se passe réellement lors de son exécution. Il s’avère que cela est simplement ignoré. Mon JIT fera donc de même. Mes cœurs d’émulateur n’ont eu aucun problème avec cette instruction, car étant indéfinie, la traiter comme si elle n’avait pas de caret était sûr, et ils n’ont donc même pas vérifié le bit indiquant cela.

Heureusement, ARM ne possède que quelques formats d’instructions. Malheureusement, ils sont tous assez complexes. La bonne nouvelle, c’est que le décodage est relativement simple. Presque chaque instruction ARM est conditionnelle, et les 4 bits supérieurs déterminent si elle s’exécute ou non. Les opérations de traitement de données utilisent toujours trois opérandes : registre de destination, registre source et « opérande », qui est le mode d’adressage 1 d’ARM. Cela peut être une valeur immédiate de certaines formes, un registre, un registre décalé par une valeur immédiate, ou un registre décalé par un autre registre. Par exemple, on peut exécuter ADD R0, R1, R2, ROR R3. Cela peut sembler intimidant ! La définition des indicateurs est optionnelle. Le chargement et le stockage de bytes ou de mots utilisent le mode d’adressage 2, qui permet d’utiliser un registre plus ou moins une valeur immédiate, ou un registre plus ou moins un autre registre, ou un registre plus ou moins un registre décalé par une valeur immédiate. Tous ces modes peuvent être indexés, post-indexés ou indexés avec écriture, ce qui permet des instructions complexes comme LDR R0, [R1], R2, LSL #12. Le chargement et le stockage de demi-mots ou de données signées utilisent le mode d’adressage 3, qui est similaire au mode 2, mais sans décalage de registre. Ce mode est également utilisé pour les instructions LDRD et STRD que certains cœurs ARMv5 implémentent (partie de l’extension DSP optionnelle). Le mode d’adressage 4 est utilisé pour les instructions LDM et STM, qui sont redoutables en raison de leur complexité et de leurs nombreux cas particuliers. Elles peuvent charger ou stocker n’importe quel sous-ensemble de registres à une adresse de base donnée avec incrémentation ou décrémentation avant ou après, et écriture optionnelle. Elles sont souvent utilisées pour les opérations de pile. Enfin, les branches sont toutes encodées de manière simple et se décodent facilement. Ouf !

Les défis de la traduction des instructions Thumb2

Au départ, on pensait que la traduction ne serait pas si difficile. Les instructions semblent similaires, et cela ne devrait pas poser trop de problèmes. Puis la réalité a frappé. Thumb2 impose de nombreuses restrictions sur les opérandes. Par exemple, SP ne peut pas être traité comme un registre général, et LR et PC ne peuvent jamais être chargés ensemble. De plus, il n’offre pas la même capacité que le mode d’adressage 1 pour décaler un registre par un autre comme troisième opérande dans une opération ALU. Il ne permet pas de décaler un troisième registre de plus de 3, contrairement au mode 2 d’ARM. Je ne vais même pas aborder les instructions LDM et STM ! De plus, il y a le problème de ne pas permettre au code traduit de savoir qu’il est en cours de traduction. Cela signifie qu’il doit toujours croire qu’il s’exécute à partir de son emplacement d’origine, et s’il se lit lui-même, il doit voir des instructions ARM. Cela implique que nous ne pouvons jamais divulguer la valeur réelle de PC dans un état exécutable. En pratique, cela signifie que nous ne pouvons jamais émettre une instruction BL, et chaque fois que PC est lu, nous devons produire une valeur immédiate équivalente à ce que PC aurait été si le code ARM avait été exécuté à son emplacement réel en mémoire. Pas très amusant…

Les instructions LDM/STM de Thumb2 manquent en fait de la moitié des modes disponibles dans ARM (modes ID et DA), ce qui nous oblige à étendre ces instructions à beaucoup plus de code. De plus, Thumb impose des limites sur l’écriture qui ne correspondent pas à celles d’ARM (plus strictes), et il est impossible d’utiliser SP dans l’ensemble des registres, ni de stocker PC de cette manière dans Thumb2. À ce stade, il devient évident que la tâche de traduire instruction par instruction ne sera pas simple. Nous aurons besoin d’endroits pour stocker des valeurs immédiates temporaires, nous devrons réécrire de nombreuses instructions, et tout cela sans provoquer d’effets secondaires. Et cela doit également être rapide !

Les complexités des opérations LDM et STM

Fonctionnement des LDM et STM en ARM

ARM dispose de deux opérations à plusieurs registres : LDM et STM. Chacune d’elles propose plusieurs modes d’adressage. Tout d’abord, il y a l’ordre : croissant ou décroissant dans les adresses (c’est-à-dire, le registre de base indique-t-il où stocker le registre le moins numéroté ou le plus élevé). Ensuite, il s’agit de savoir si le registre de base doit être utilisé tel quel ou s’il doit être incrémenté ou décrémenté au préalable. Cela nous donne les quatre modes de base : IA (« incrément après »), IB (« incrément avant »), DA (« décrément après »), DB (« décrément avant »). De plus, il est optionnel de mettre à jour l’adresse de base dans le registre de base. Bien sûr, il existe des cas particuliers, comme la valeur qui est stockée si le registre de base avec mise à jour est utilisé, ou quelle valeur le registre de base aura s’il est chargé alors que la mise à jour est également spécifiée. La spécification ARM définit explicitement certains de ces cas comme ayant des conséquences imprévisibles.

Pour la pile, ARM utilise une pile descendante complète. Cela signifie qu’à tout moment, le registre SP pointe vers la dernière position de pile déjà utilisée. Ainsi, pour dépiler une valeur, vous la chargez depuis [SP], puis vous incrémentez SP de 4. Cela se fait en utilisant une instruction LDM.

Comprendre le fonctionnement des instructions LDM/STM dans Thumb2

Pour introduire le sujet, il est essentiel de comprendre comment les valeurs sont gérées dans la pile. Pour ajouter une valeur à la pile, il faut d’abord diminuer le registre de pile (SP) de 4, puis stocker la valeur souhaitée à l’adresse indiquée par SP. Cela correspond à une instruction STM utilisant un mode d’adressage DB. Les modes IB et DA ne sont généralement pas utilisés pour la gestion de la pile dans le code ARM classique.

Les limitations de Thumb2

Pourquoi est-ce important ? Lors de la conception de l’ensemble d’instructions Thumb2, ARM a fait des choix sur les fonctionnalités à inclure. Cela a conduit à l’exclusion de certaines options moins courantes. En effet, Thumb2 ne prend pas en charge les modes IB et DA. De plus, il est interdit d’utiliser les registres PC ou SP dans la liste des registres à stocker lors d’une instruction STM. Il est également impossible de charger SP avec LDM, et si une instruction LDM charge PC, elle ne peut pas charger LR en même temps, et vice versa. En outre, PC ne peut pas être utilisé comme registre de base, et la liste des registres doit contenir au moins deux éléments. Cela constitue une liste partielle des limitations de Thumb2 par rapport à ARM.

Complexité de la traduction des instructions

Les instructions qui se traduisent bien d’ARM à Thumb2 ne sont pas toujours simples à convertir. Par exemple, le stockage de PC est complexe, car il faut un registre temporaire pour conserver la valeur attendue de PC avant de l’ajouter à la pile. Les registres sont empilés dans un ordre précis, donc le choix du registre temporaire peut affecter la relative position des autres registres, nécessitant parfois de diviser le stockage en plusieurs opérations. Si le stockage implique SP, il faut également ajuster en conséquence. Dans le cas d’une instruction STMDB SP (c’est-à-dire PUSH), il devient difficile de préempiler un registre temporaire.

Les défis des instructions atomiques

Une autre complication réside dans le fait que LDM/STM est censé agir comme une instruction atomique pour l’espace utilisateur. Cela signifie qu’elle doit être soit annulée, soit reprise au niveau système. Cependant, dans les puces Cortex-M utilisant Thumb2, SP a une importance particulière, car le cadre d’exception y est stocké. Cela implique que SP doit toujours être valide, et toute donnée stockée en dessous de SP n’est pas garantie de persister, car une interruption peut survenir à tout moment. Heureusement, sur ARM, il était également déconseillé de stocker des données en dessous de SP, ce qui était rare. Un exemple notoire est un morceau de code PalmOS qui le fait, mais pour d’autres raisons, ce code a été remplacé. Dans tous les autres cas, le JIT émettra un avertissement si une tentative de chargement ou de stockage en dessous de SP est effectuée.

La complexité de la traduction LDM/STM

- Vérifier si l’instruction entraîne un comportement indéfini ou n’est pas définie selon le Manuel de Référence de l’Architecture ARM. Si c’est le cas, enregistrer une erreur et abandonner.

- Déterminer si elle peut être émise comme une instruction Thumb2 LDM/STM, c’est-à-dire si elle respecte toutes les restrictions imposées par Thumb2, et si PC n’est pas stocké, émettre une instruction Thumb2 LDM/STM.

- Vérifier si elle peut être émise comme LDR/STR/LDRD/STRD tout en respectant les limites de Thumb2. Si c’est le cas, émettre cette instruction.

- Traiter quelques cas spéciaux pour des traductions rapides d’instructions courantes non couvertes par les étapes précédentes.

- Pour les modes non pris en charge IB et DA, s’ils ne nécessitent pas de retour d’écriture, ils peuvent être réécrits en termes de modes pris en charge.

- Si l’instruction charge SP, il est impossible d’émettre une traduction valide en raison de l’utilisation de SP dans ARMv7-M. Pour ce cas particulier, le JIT émet une instruction indéfinie et nous l’imitons. Heureusement, aucun code courant ne l’utilise !

- Enfin, suivre le chemin générique lent :

- Générer une liste de registres à charger/stocker et à quelles adresses.

- Calculer le retour d’écriture si nécessaire.

- Si besoin, allouer un ou deux registres temporaires (deux si PC et SP sont stockés) et sauvegarder leur contenu sur la pile.

- Pour tous les registres restants à charger/stocker, déterminer combien peuvent être chargés/stokés simultanément et procéder. Cela implique d’émettre une série d’instructions : LDR/STR/LDRD/STRD/LDM/STM jusqu’à ce que tout soit fait.

- Si des registres temporaires ont été alloués, les restaurer.

Instructions conditionnelles et leur complexité

Les modes d’adressage complexes, notamment le mode 1, posent également des défis. Grâce aux modes de rotation par registre, un registre temporaire est nécessaire pour calculer la valeur avant de l’utiliser. Si le registre de destination n’est pas utilisé, il peut servir de stockage temporaire, à condition qu’il ne soit pas également l’un des autres opérandes sources, ou SP, ou PC. Cela complique encore la situation. Si PC est également un opérande, un registre temporaire est requis pour charger la valeur « factice » de PC avant de pouvoir effectuer des opérations. Cela peut rapidement devenir un casse-tête. Pour plus de détails, consultez « emuJit.c ». nous faisons de notre mieux pour éviter de déverser des données sur la pile, mais parfois, cela s’avère inévitable.

Cette complexité s’applique également à certains modes d’adressage complexes. Thumb2 a optimisé ses instructions pour les cas courants, rendant les cas moins fréquents très difficiles à traduire. Il est encore plus difficile de trouver des registres temporaires, car si nous empilons quoi que ce soit, nous devons en tenir compte si notre registre de base est SP. les traductions efficaces sont réservées aux cas courants, tandis que les cas rares sont souvent négligés. Un cas particulier concerne les chargements basés sur PC, utilisés pour charger des données constantes. Dans la plupart des cas, nous intégrons les données constantes dans les traductions produites pour des raisons de rapidité.

Instructions Conditionnelles dans Thumb2

Le système Thumb2 offre des mécanismes pour établir des instructions conditionnelles grâce à l’instruction IT, qui permet de rendre les 1 à 4 instructions suivantes conditionnelles. J’ai choisi de ne pas l’utiliser, car cela modifie également la manière dont les indicateurs sont définis par les instructions Thumb de 2 octets, et je ne souhaitais pas créer des cas particuliers. De plus, il arrive que 4 instructions ne suffisent pas pour une traduction complète. Par exemple, certaines instructions STMDA peuvent s’étendre sur environ 28 instructions. Dans ces cas, j’émet un saut de polarité opposée (condition) sur la traduction. Cela fonctionne, car ces sauts ne font également que 2 octets pour toutes les longueurs de traduction possibles.

Sauts et Appels

Ce domaine est particulièrement fascinant. En gros, il existe deux types de sauts/appels : ceux dont les destinations sont connues au moment de la traduction et ceux dont elles ne le sont pas. Les sauts avec des adresses connues sont relativement simples à gérer. Nous recherchons l’adresse de destination dans notre TC. Si elle est trouvée, nous émettons un saut direct vers cette unité de traduction (TU). Cela rend les boucles fréquentes très rapides, car aucune sortie du code traduit n’est nécessaire. Les sauts indirects ou calculés sont moins courants, ce qui pourrait laisser penser qu’ils ne sont pas très importants. Cependant, c’est une erreur, car un type de saut indirect se produit fréquemment : le retour de fonction. Au moment de la traduction, nous ne savons pas où le retour va se diriger. Comment gérons-nous cela ? Si le code charge directement PC, tout fonctionne comme prévu. Soit il s’agit d’une adresse ARM et notre gestionnaire UsageFault s’en occupera, soit il s’agit d’une adresse Thumb et notre CPU y sautera directement. Une optimisation existe pour le cas où une instruction BX LR est rencontrée. Nous émettons alors un saut direct vers une fonction qui recherche LR dans le hachage, ce qui nous fait gagner le temps nécessaire pour gérer une exception et y revenir (environ 60 cycles). D’autres optimisations sont possibles et seront ajoutées, mais pour l’instant, c’est ainsi que cela fonctionne. Que faire pour un saut dont la destination est connue mais qui n’a pas encore été traduite ? Nous laissons un marqueur, c’est-à-dire une instruction que nous savons être indéfinie, suivie de l’adresse cible. Ainsi, si le saut est effectivement pris (ce qui n’est pas toujours le cas), nous prendrons l’exception, traduirons, puis remplacerons cette instruction indéfinie et le mot qui la suit par un saut réel. La prochaine fois, ce saut sera rapide, sans provoquer d’exceptions.

Processus de Traduction d’une TU

Le processus est simple : nous traduisons les instructions jusqu’à atteindre une instruction que nous considérons comme terminale. Qu’est-ce qui est terminal ? Un saut inconditionnel est terminal. Un appel l’est aussi (qu’il soit conditionnel ou non). Pourquoi ? Parce qu’il se peut que quelqu’un revienne de cet appel, et nous préférons que le code de retour soit dans une nouvelle TU afin de pouvoir le retrouver lors du retour. Une écriture inconditionnelle dans PC de quelque sorte que ce soit est également terminale. Il y a une astuce pour les sauts vers des endroits proches. En traduisant une TU, nous gardons une trace des dernières instructions traduites et de leurs traductions. Ainsi, si nous voyons un saut court en arrière, nous pouvons littéralement intégrer un saut vers cette traduction, créant ainsi une traduction très rapide de cette petite boucle. Mais qu’en est-il des sauts courts en avant ? Nous les mémorisons également, et si avant d’atteindre notre instruction terminale, nous traduisons une adresse que nous avons mémorisée d’un saut précédent dans cette même TU, nous retournerons et remplacerons ce saut par un saut court vers ici.

Que faire si le TC est plein ?

Vous aurez peut-être remarqué que j’ai mentionné que nous émettons des sauts entre les TUs. « Cela ne signifie-t-il pas, » pourriez-vous demander, « que vous ne pouvez pas simplement supprimer une TU ? » C’est exact. Il s’avère que suivre quelles TUs sont beaucoup utilisées et lesquelles ne le sont pas est trop complexe, et les avantages des sauts inter-TU sont trop importants pour être ignorés. Que faisons-nous donc lorsque le TC est plein ? Nous le vidons – nous le jetons littéralement. Cela aide également à s’assurer que les anciennes traductions qui ne sont plus nécessaires sont finalement éliminées. Le TC de chaque thread croît jusqu’à une taille maximale. Certains threads n’exécutent jamais beaucoup d’ARM et finissent avec des TCs petits. Le TC du thread principal de l’interface utilisateur atteindra pratiquement toujours la taille maximale (actuellement 32 Ko).

Améliorations du JIT

Après avoir mis en place le JIT, j’ai entrepris de le réécrire. La version initiale contenait de nombreuses valeurs magiques et des lacunes (des cas qui pouvaient se produire dans un code légitime mais qui seraient mal traduits). Elle émettait parfois des opcodes invalides que le Cortex-M4 exécutait malgré les documents indiquant qu’ils n’étaient pas autorisés. Le JIT a été divisé en deux parties. La première était le frontend qui ingérait les instructions ARM, maintenait le TC et suivait divers autres états. La seconde était le backend. Le backend avait une fonction pour chaque mode d’adressage ARMv5 ou format d’instruction possible, et pour toute instruction ARMv5 valide, il pouvait produire une séquence d’instructions ARMv7M pour accomplir la même tâche. Pour les cas courants, la séquence était bien optimisée, tandis que pour les cas moins fréquents, elle ne l’était pas. Cependant, le backend gère TOUTE demande ARMv5 valide possible, même des instructions étranges comme RSBS PC, SP, PC, ROR SP. Personne de sensé ne produirait jamais cette instruction, mais le backend la traduira correctement. J’ai écrit des tests et les ai exécutés automatiquement pour vérifier que toutes les entrées possibles sont traitées correctement. J’ai également optimisé le chemin le plus fréquent dans tout le système – l’émulation de l’instruction BLX en mode Thumb. Cela a permis un gain de 50 cycles, ce qui a eu un impact notable sur les performances. En outre, j’ai remarqué que souvent, le code Thumb utilisait un BLX simplement pour sauter à un OsCall (qui, en raison de l’utilisation de R12 et R9, ne peut pas être écrit en mode Thumb). Le nouveau gestionnaire BLX détecte cela et évite l’émulation en appelant directement l’OsCall requis.

J’ai ensuite développé un sous-backend pour l’extension EDSP (instructions ARMv5E) car certaines applications Sony les utilisent. La raison d’un sous-backend séparé est que l’ARMv7E (Cortex-M4) dispose d’instructions que nous pouvons utiliser pour traduire les instructions EDSP de manière très efficace, tandis que l’ARMv7 (Cortex-M3) ne le fait pas et nécessite des séquences d’instructions plus longues pour accomplir le même travail. rePalm prend en charge les deux.

Plus tard, j’ai revisité le code et, malgré la complexité, j’ai trouvé un moyen d’utiliser l’instruction IT sur Cortex-M3+. Cela a entraîné une refonte massive du code – en gros, en poussant le « code conditionnel » dans chaque fonction backend et en s’attendant à ce qu’elle se conditionne comme elle le souhaite. Cela a produit un changement avec un diff de plus de 4000 lignes, mais cela fonctionne très bien et a entraîné une augmentation de la vitesse !

Le Backend Cortex-M0

Pourquoi c’est un défi

C’était un véritable défi, mais je voulais voir si je pouvais créer un backend fonctionnel pour Cortex-M0 dans mon JIT. Le Cortex-M0 exécute l’ensemble d’instructions ARMv6-m. Cela correspond essentiellement à Thumb-1, avec quelques ajouts mineurs. Pourquoi cela est-il préoccupant ? Dans Thumb-1, la plupart des instructions n’ont accès qu’à la moitié des registres (r0..r7). Seules trois instructions ont accès aux registres supérieurs : CMP, MOV et ADD. Presque toutes les instructions Thumb-1 définissent toujours des indicateurs. De plus, il n’existe pas d’instructions de multiplication longue dans Thumb-1. Et il n’y a pas de mode de rotation RRX du tout. La confluence de tous ces problèmes rend la tentative d’une traduction instruction par instruction de l’ARM vers Thumb-1 pratiquement impossible.

Les Fondamentaux

Les registres r0 à r3 sont des registres de travail temporaires pour nous. Le registre r4 est l’endroit où nous stockons notre contexte (l’endroit où nous conserverons l’état supplémentaire). De plus, pour des raisons de rapidité, nous aurons besoin d’un registre pour stocker le registre d’état virtuel. Pourquoi en avons-nous besoin ? Parce que presque toutes nos instructions Thumb-1 modifient les indicateurs, tandis que le code ARM que nous traduisons s’attend à ce que les indicateurs restent valides pendant de longues séquences d’instructions. Ainsi, notre total est de 6. Nous avons besoin de 6 registres. Ils doivent être des registres bas, car, comme nous l’avons discuté, les registres supérieurs sont pratiquement inutiles dans Thumb-1.

Technologie : La rapidité de PACE est-elle suffisante ?

Les sauts indirects…

Malheureusement, l’émulation implique presque toujours de nombreux sauts indirects. C’est en effet la méthode utilisée pour le décodage des instructions. L’architecture 68k, étant une architecture CISC avec des instructions de longueur variable, rend cette étape de décodage complexe. L’émulateur de PACE est clairement écrit à la main en assembleur, avec quelques astuces. Il s’agit d’un code entièrement ARM, et il est identique instruction par instruction de PalmOS 5.0 à PalmOS 5.4. Bien que le code environnant ait changé, le cœur de l’émulateur est resté inchangé. C’est une bonne nouvelle, car cela signifie qu’il était déjà performant. Mon JIT gère correctement la traduction de PACE, comme en témoigne le fait que rePalm fonctionne sur ARMv7-M. Le principal problème réside dans le fait que chaque instruction émulée nécessite au moins un saut indirect (pour les instructions courantes), deux pour celles de fréquence moyenne, et jusqu’à trois pour certaines rares. En raison du fonctionnement de mon JIT, chaque saut indirect qui n’est pas un retour de fonction nécessite une exception (14 cycles à l’entrée, 12 à la sortie), un code d’assemblage supplémentaire (~30 cycles) et une recherche de hachage (~20 cycles). Ainsi, même si le code cible a été traduit, cela ajoute environ 70 cycles à chaque saut indirect. Cela limite l’efficacité de l’émulateur 68k à un rapport de 1/70 de la vitesse. Ce n’est pas idéal. En général, PACE fonctionne à environ 1/15 de la vitesse du code natif, ce qui représente un ralentissement significatif. J’ai envisagé d’écrire une meilleure traduction spécifiquement pour PACE, mais cela s’avère assez complexe. En effet, il n’existe pas de méthode simple et rapide pour traduire des instructions comme LDR R0, [R11, R1, LSL #2]; ADD PC, R11, R0. Il est impossible de savoir où ce saut ira, ou même si R11 pointe vers un emplacement immuable. Malheureusement, c’est exactement ce à quoi ressemble le dispatching de haut niveau de PACE.

Une solution spéciale pour un problème particulier

J’avais déjà atteint mon objectif de faire fonctionner PalmOS sans modifications – PACE fonctionne avec mon JIT, et le système d’exploitation est utilisable et réactif. Cependant, je souhaitais une solution améliorée, car je considérais que PACE représentait un problème suffisamment unique pour justifier des efforts supplémentaires. L’émulateur de code dans PACE a un point d’entrée unique et n’appelle d’autres codes que dans dix cas précis : Line1010 (instructions commençant par 0xA), Line1111 (instructions commençant par 0xF), TRAP0, TRAP8, TRAPF (OsCall), Division par zéro, Instruction illégale, Instruction non implémentée, Bit de trace activé, et atteinte d’une valeur PC de 0xFFFFFFF0. Que faire alors ? J’ai développé un outil appelé « patchpace » qui prend un fichier PACE.prc de n’importe quel appareil PalmOS, l’analyse pour localiser ces gestionnaires dans le binaire, et identifie le cœur principal de l’émulateur. Il remplace ensuite ce cœur (sur place si l’espace le permet, sinon en l’ajoutant au binaire) par le code que vous fournissez. Les adresses des gestionnaires seront insérées dans votre code aux offsets fournis par l’en-tête, et un saut vers votre code sera placé à l’endroit où se trouvait l’ancien cœur de l’émulateur. L’en-tête est très simple (voir « patchpace.c ») et inclut juste des offsets de demi-mots depuis le début du binaire jusqu’à l’entrée, et vers les sauts vers chacun des gestionnaires mentionnés sous forme d’instructions BL ou BLX. Le seul paramètre pour l’émulateur est l’état. Il est structuré comme suit : le premier mot est libre pour l’utilisation de l’émulateur, suivi de 8 registres D, puis de 8 registres A, ensuite le PC, et enfin le SR. Aucun autre donnée n’est autorisée (PACE utilise des données après cela). Ce même état doit être transmis à tous les gestionnaires. Le gestionnaire TRAPF a également besoin que le mot suivant lui soit transmis (numéro OsCall). Oui, vous avez bien compris, cela vous permet d’apporter votre propre émulateur 68k à la fête. N’importe quel émulateur 68k fera l’affaire, il n’a pas besoin de connaître quoi que ce soit sur PalmOS. Plutôt intéressant, non ?

N’importe quel émulateur 68k…

Alors, où peut-on se procurer un émulateur 68k ? Eh bien, n’importe où ! J’ai écrit un émulateur simple en C pour tester cette idée, et cela a bien fonctionné, mais pour ce genre de projet, vous souhaitez utiliser de l’assembleur. J’ai pris l’émulateur de PACE comme guide de style et j’ai réalisé un travail considérable pour produire un émulateur 68k en thumb2. Il est beaucoup plus efficace que ce que PACE a jamais été. Cela est inclus dans le dossier « mkrom » sous le nom « PACE.0003.patch ». Comme mentionné précédemment, cela est entièrement optionnel et non requis. Cependant, cela améliore la vitesse brute du 68k d’environ 8,4 fois dans les cas typiques.

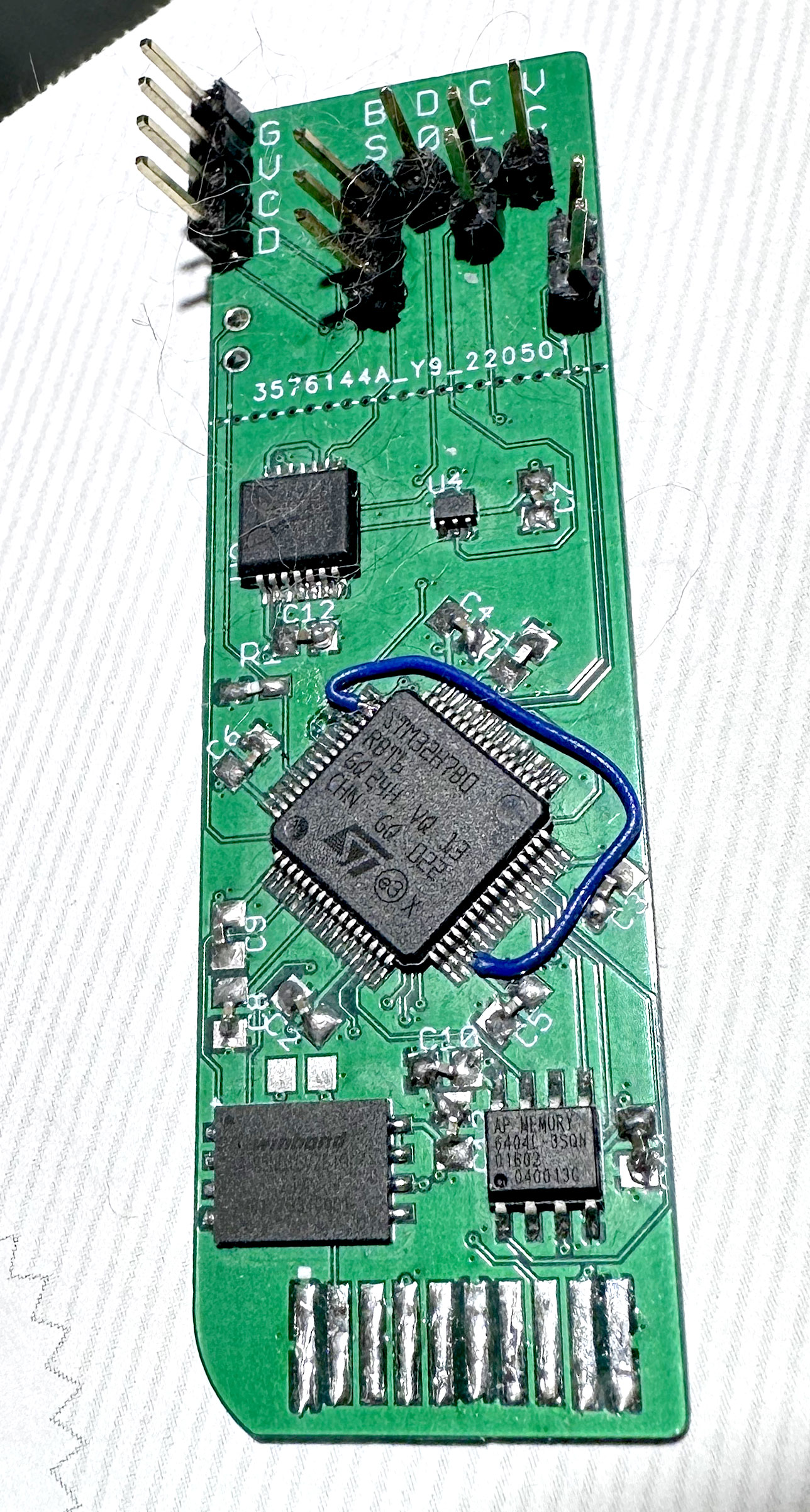

Technologie : Mais vous aviez promis du matériel…

Le matériel a ses défauts

J’avais besoin d’une carte de développement pour expérimenter. La carte de découverte STM32F429 semblait être un bon choix. Elle dispose de 8 Mo de RAM, ce qui est suffisant, de 2 Mo de flash, ce qui est bon, et d’un écran avec un écran tactile. En théorie, c’est parfait. Oh, si seulement j’avais su à quel point la réalité était imparfaite. En consultant le manuel de référence du STM32F429, il semble que ce soit la puce idéale pour ce projet. Cependant, ST ne fait pas vraiment d’efforts pour vous indiquer où se trouvent les problèmes. La feuille d’errata est accablante. En gros, si vous faites fonctionner le CPU à partir de la mémoire externe, placez la pile dans la mémoire externe, et que le FIFO SDRAM est activé, les exceptions feront planter la puce (lecture incorrecte de l’adresse de vecteur). D’accord, je peux contourner cela – il suffit de désactiver le FIFO. Problème suivant : même histoire, mais si le FIFO est désactivé, parfois les écritures seront…

Défis et Solutions dans l’Ingénierie Inverse de PalmOS

Problèmes de RAM et de Gestion des Interruptions

Il est frustrant de constater que, malgré mes efforts pour transférer mes données vers la RAM interne, des plantages continuent de se produire. Après avoir retiré rePalm et mis en place un scénario de reproduction de 20 lignes, j’ai découvert un problème non documenté dans les notes de version de ST. Lorsque le registre PC pointe vers la RAM externe et que l’instruction WFI est exécutée pour attendre des interruptions en mode basse consommation, si une interruption survient après plus de 60 ms, le processeur sélectionne un vecteur d’interruption aléatoire au lieu du bon. Cela a nécessité de nombreuses nuits blanches à déchiffrer des plantages aléatoires dans les gestionnaires d’interruptions, qui ne devraient pas être actifs à ce moment-là. J’ai contourné ce problème en évitant d’utiliser WFI, ce qui entraîne un gaspillage d’énergie, mais cela est acceptable pour le développement jusqu’à ce que je conçoive une carte avec un chip fonctionnel.

Problèmes d’Adresse de RAM

Le STM32F429 prend en charge deux banques de RAM, 0 et 1, avec la banque 0 commençant à 0xC0000000 et la banque 1 à 0xD0000000. Cela pose un problème, car PalmOS exige que la RAM et la mémoire flash soient en dessous de 0x80000000. Heureusement, la banque 0 peut être remappée à 0x00000000. Cependant, la conception de la carte laisse à désirer, car elle ne dispose que d’une seule puce RAM, qui est logiquement la banque 0. En réalité, c’est la banque 1 qui est utilisée, et celle-ci ne peut pas être remappée. Cela rend la carte inutilisable pour démarrer PalmOS, car la limite de 0x80000000 est rigide.

Pourquoi la Limite de 0x80000000 ?

PalmOS gère deux types de blocs de mémoire : les blocs mobiles et non mobiles. Cette distinction est essentielle pour un système d’exploitation sans unité de gestion de mémoire (MMU) afin d’éviter une fragmentation excessive. Lorsqu’un bloc mobile n’est pas verrouillé, l’OS peut le déplacer, et il est référencé par un « handle ». On peut ensuite le verrouiller pour obtenir un pointeur, l’utiliser, puis le déverrouiller. La limite de 0x80000000 est cruciale, car PalmOS utilise le bit supérieur d’un pointeur pour indiquer s’il s’agit d’un handle ou d’un pointeur réel. Si le bit supérieur est activé, cela signifie un handle ; s’il est désactivé, c’est un pointeur. Ainsi, il est impossible d’avoir à la fois la RAM et la ROM au-dessus de 0x80000000.

Des Solutions Innovantes aux Problèmes de Conception

Étant donné que cette carte est destinée à un développement temporaire, pourquoi ne pas aller plus loin ? La distinction entre handle et pointeur n’est vérifiée qu’à quelques endroits. J’ai donc décidé de modifier ces vérifications pour inverser la condition, du moins temporairement. J’ai désassemblé et corrigé manuellement 58 emplacements, principalement dans Boot, où se trouve le MemoryManager, et quelques-uns dans UI, car le code des champs de texte doit déterminer si un pointeur passé est un pointeur (non modifiable) ou un handle (modifiable). J’ai également effectué des modifications dans PACE, qui avait un SysTrap pour déterminer le type de pointeur. Bien que cela ne soit plus « PalmOS non modifié », cela reste temporaire. Cependant, cela soulève une question : si nous inversions la condition, cela nécessiterait que la RAM et la ROM soient toutes deux au-dessus de 0x80000000. Mais la mémoire flash est à 0x08000000… Oups. Cela signifie que nous ne pouvons plus utiliser la mémoire flash. J’ai donc modifié la disposition de la RAM, réservant 2 Mo à 0xD0600000 pour simuler la « ROM » et j’y copie la flash au démarrage. Cela fonctionne !

Support de la Carte SD

Heureusement, j’avais déjà développé un pilote de slot pour PalmOS, donc la création d’un pilote pour carte SD n’a pas été difficile. J’ai même réutilisé une partie du code source de PowerSDHC ! Le support des cartes SD est désormais opérationnel sur la carte de développement STM32F469. Sur la carte STM32F429, bien qu’elles soient également prises en charge, il faut les câbler soi-même, car la carte ne dispose pas de slot (CLK -> C12, CMD -> D2, DAT_0 -> C8). En raison de la configuration de la carte, seul un bus d’un bit fonctionne, ce qui limite la vitesse à environ 4 Mbit/s sur la STM32F429, tandis que sur la STM32F469, la vitesse atteint 37 Mbit/s. Des vitesses plus élevées pourraient être atteintes avec DMA, mais cela est suffisant pour le moment. En développant le support de la carte SD pour les puces STM32F4, j’ai découvert un bug matériel difficile à déboguer. le bus SD permet à l’hôte d’arrêter l’horloge à tout moment, mais cela pose des problèmes lorsque la carte est occupée, car elle attend un signal d’horloge pour changer l’état de la ligne DAT_0. J’ai donc désactivé la fonction d’arrêt automatique de l’horloge après une semaine de débogage, ce qui a nécessité une simple correction d’une ligne. Le pilote de slot est disponible dans le répertoire « slot_driver_stm32 ».

Support du Port Série

Palm Inc a documenté la création d’un pilote de port série pour PalmOS 4, avec deux types : les pilotes virtuels et les pilotes série. Les premiers étaient destinés aux ports non câblés (comme le port Bluetooth ou infrarouge), tandis que les seconds étaient pour les ports câblés (comme le port série du socle). PalmOS 5 a fusionné ces deux types en un type « virtuel » unifié, mais cela n’a pas été documenté. J’ai dû effectuer une ingénierie inverse prolongée pour comprendre son fonctionnement. J’ai produit une idée fonctionnelle de ce système sur PalmOS 5, que vous pouvez consulter dans le fichier d’inclusion « vdrvV5.h ». Ces informations suffisent pour créer un pilote fonctionnel pour un port série, un port IrDA SIR et USB pour les synchronisations.

La mise en œuvre du port série sur le matériel STM32F4 a été un défi. Le matériel ne dispose que d’un seul tampon d’un octet, ce qui signifie qu’il faut utiliser le contrôle de flux matériel ou faire en sorte que l’interruption du port série soit de la plus haute priorité pour éviter de perdre des données à des débits élevés. Cela n’était pas acceptable pour moi, j’ai donc opté pour le DMA. Cela m’a permis d’écrire ma première bibliothèque PalmOS 5 pouvant être utilisée par d’autres bibliothèques. J’ai développé une bibliothèque DMA pour les puces de la série STM32F4, disponible dans le répertoire « dma_driver_stm32 ». Cependant, le DMA nécessite de savoir combien d’octets vous attendez de recevoir, ce qui pose problème pour les données UART génériques. J’ai donc utilisé une approche astucieuse : le DMA peut nous interrompre lorsque la moitié d’un transfert est terminée, puis à nouveau lorsque tout est terminé. Le DMA peut être circulaire, ce qui nous permet de redémarrer au début une fois le transfert terminé. Cela nous rapproche de la solution idéale tant que les données continuent d’arriver.

Gestion des Interruptions et Réception de Données

Lorsqu’il s’agit de gérer les interruptions, il est essentiel de s’assurer que notre système peut traiter les données efficacement. Dans notre gestionnaire d’interruptions, il est crucial de vérifier la position actuelle dans le tampon et de signaler les octets reçus depuis notre dernière vérification comme de nouvelles données. Cependant, un problème se pose si nous ne recevons qu’un seul octet. Cela représente moins de la moitié d’un transfert, ce qui signifie qu’aucune interruption ne sera générée, et nous ne pourrons pas signaler cette donnée aux clients. Cette situation est inacceptable. Heureusement, le mode « détection IDLE » du UART STM32F4 résout ce problème. Ce mode déclenche une interruption si, après la réception d’un octet, quatre temps de bits s’écoulent sans qu’un nouveau caractère ne commence. En intégrant cette interruption à notre code de gestion du tampon circulaire, nous pouvons recevoir des données à la vitesse à laquelle elles arrivent, peu importe leur taille. Mon pilote série, que vous pouvez trouver dans le répertoire « uart_driver_stm32 », fonctionne parfaitement et a même permis une synchronisation à chaud. Le support IrDA est également inclus, et tout fonctionne de manière fluide. Consultez l’album photo pour une démonstration vidéo !

Essayez-le vous-même !

Pour ceux qui souhaitent expérimenter sur la carte de découverte STM32F429, le trou non peuplé de 0,1 pouce étiqueté « RX » est en réalité la sortie de transmission du STM32 (une étiquette quelque peu déroutante pour une broche de transmission). La broche B7 est celle de réception. En connectant un adaptateur USB-série, vous pourrez effectuer une synchronisation à chaud via le port série. Si vous optez pour un émetteur-récepteur IrDA SIR, vous obtiendrez également un fonctionnement IR. J’ai utilisé le transceiver MiniSIR2 de Novalog, Inc., qui est le même que celui utilisé par la plupart des appareils Palm.

Support de Vibration et de LED

Le support de la vibration et des LED n’a jamais été documenté, car ce sont des fonctionnalités matérielles gérées par les fournisseurs. Heureusement, j’avais déjà effectué une rétro-ingénierie de ces fonctionnalités lorsque j’ai ajouté le support de vibration au T|X. Il s’avère que j’avais presque tout compris à l’époque. Un peu plus de rétro-ingénierie a permis d’obtenir un résultat complet concernant l’API appropriée. Le fonctionnement des LED suit le même principe que celui des vibreurs : une fonction « GetAttributes » et une fonction « SetAttributes ». Les paramètres réglables incluent le motif, la vitesse, le délai entre les répétitions et le nombre de répétitions. Le système d’exploitation les utilise selon les besoins et ajoute automatiquement les paramètres »Vibrer » et « LED » au panneau de préférences « Sons et Alertes » si le matériel est pris en charge. Et rePalm prend désormais en charge les deux ! Le code est disponible dans « halVibAndLed.c », n’hésitez pas à l’explorer à votre convenance.

Support Réseau (En Cours de Développement)

Débuts Difficiles

Mon objectif était d’ajouter un support réseau à rePalm. Plusieurs méthodes me venaient à l’esprit pour garantir la compatibilité avec les applications existantes. Une option serait de remplacer Net.lib par une version ayant une interface similaire, mais sous mon contrôle. Cela me permettrait de le connecter à n’importe quelle interface de mon choix, rendant tout cela magique. Cependant, cette approche présente des inconvénients. Bien que de nombreuses parties de Net.lib soient documentées, d’autres ne le sont pas, rendant leur compréhension difficile. De plus, il est essentiel de faire fonctionner un PalmOS non modifié, et remplacer des bibliothèques aléatoires compromet cette capacité. Cette méthode ne serait donc pas viable. Une autre possibilité serait de créer une interface série fictive et de demander à PalmOS de s’y connecter via SLIP ou PPP à une machine distante fictive. L’autre extrémité de ce port série pourrait être reliée à un thread communiquant avec notre véritable interface réseau. Bien que cela soit réalisable, cela impliquerait des surcharges de codage et de décodage des trames PPP/SLIP, et l’interface utilisateur serait confuse. Trouver des moyens de configurer l’interface serait également un défi. Mais peut-être existe-t-il une meilleure solution ?

Une Voie Difficile mais Prometteuse

Sur le plan conceptuel, une meilleure approche existe. Le Net.lib de PalmOS prend en charge des interfaces réseau modulables (que j’appelle un pilote NetIF). On peut en trouver plusieurs sur tous les appareils PalmOS : PPP, SLIP, Boucle de retour. Certains autres modèles disposent également d’une interface pour le WiFi ou le réseau cellulaire. Il me suffit donc de produire un pilote NetIF. Cela semble simple, n’est-ce pas ? En réalité, la réponse est un « non » retentissant ! Écrire des pilotes NetIF n’a jamais été documenté, et une interface réseau est beaucoup plus complexe qu’un pilote de port série (qui était l’interface de pilote précédente de PalmOS que j’avais rétro-ingénierie). La rétro-ingénierie de cela s’avère être un défi considérable.

Apprendre de l’Histoire